Planche d'Exercices N<sup>0</sup>1 Circuits Combinatoires L1 - MI – S2 / 2019-2020

Le savoir qui compte est celui qu'on se donne soi-même par curiosité, passion de savoir. P. Léautaud

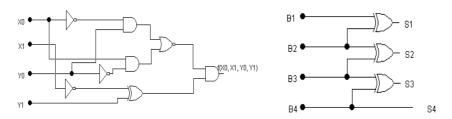

### Exercice 1 : Analyser les circuits logiques suivants :

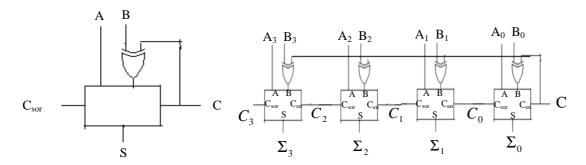

<u>Exercice 2</u>: Concevoir un circuit qui permet de faire l'addition ou la soustraction (additionneur/soustracteur) de deux nombres binaires A et B de 1 bit. On rappelle que dans la représentation en complément à 2,  $A - B = A + \overline{B} + 1$ . Cet additionneur/soustracteur possèdera une entrée de commande C qui sera utilisée comme suit :

- C=0, fonctionnement en addition.

- C=1, fonctionnement en soustraction.

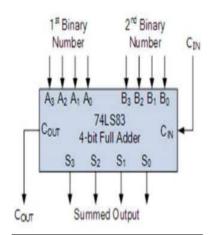

En utilisant ce schéma bloc de additionneur-soustracteur, dessiner un schéma bloc d'un additionneur – soustracteur en parallèle à 4 bits, c'est-à-dire un circuit logique qui peut faire la somme des nombres binaires  $A = A_3 A_2 A_1 A_0$  et  $B = B_3 B_2 B_1 B_0$  si C = 0 et A - B si C = 1.

#### Exercice 3

1. Soit la fonction combinatoire f(x,y,z) définie par la table de Karnaugh ci dessous

| ab | 00 | 0 1 | 11 | 10 |

|----|----|-----|----|----|

| 0  | 1  | 0   | 1  | 1  |

| 1  | 1  | 1   | 1  | 0  |

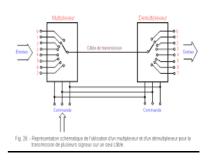

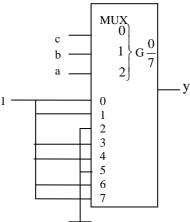

- 1. Synthétiser cette fonction avec un multiplexeur  $8 \rightarrow 1$ .

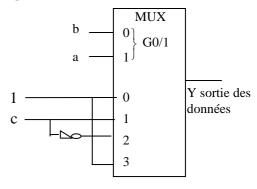

- 2. Synthétiser cette fonction avec un multiplexeur  $4 \rightarrow 1$ .

### **Exercice 4**

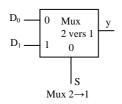

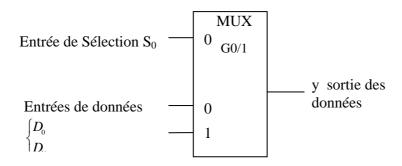

Faire la synthèse d'un multiplexeur 2 vers 1. En utilisant le schéma bloc ci-dessous, réalisé le schéma bloc d'un multiplexeur 4 vers 1 en utilisant que trois multiplexeurs 2 vers 1.

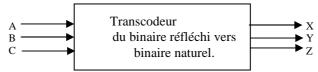

### Exercice 5

On veut réaliser un transcodeur permettant de convertir un nombre en binaire réfléchi de trois bits ABC vers le binaire naturel XYZ. Ce transcodeur a trois entrées : A, B et C et trois sorties X, Y et Z.

- 1. Dresser une table de vérité traduisant le fonctionnement,

- 2. A l'aide du tableau de Karnaugh, trouver les équations des sorties : X, Y et Z,

- 3. Donner le logigramme de ce transcodeur.

- 4. Dessiner le logigramme avec uniquement des portes "XOR" à deux entrées,

- 5. En déduire le logigramme si le code d'entrée est sur 4 bits.

### **Annexe**

### Corrigé série 1

### Exercice 1

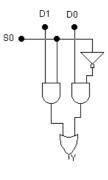

1. Expression logique :  $f(x_0, x_1, y_0, y_1) = \overline{\overline{x_0}.y_0 + x_0.\overline{y_0}}.(\overline{x_1} \oplus y_1) = \overline{x_0} \oplus y_0.(\overline{x_1} \oplus y_1)$ . Table de vérité

| $x_0$ | <i>x</i> <sub>1</sub> | $y_0$ | $y_1$ | $\overline{x_0 \oplus y_0}$ | $(\overline{x_1} \oplus y_1)$ | $f(x_0, x_1, y_0, y_1)$ |

|-------|-----------------------|-------|-------|-----------------------------|-------------------------------|-------------------------|

| 0     | 0                     | 0     | 0     | 1                           | 1                             | 1                       |

| 0     | 0                     | 0     | 1     | 1                           | 0                             | 0                       |

| 0     | 0                     | 1     | 0     | 0                           | 1                             | 0                       |

| 0     | 0                     | 1     | 1     | 0                           | 0                             | 0                       |

| 0     | 1                     | 0     | 0     | 1                           | 0                             | 0                       |

| 0     | 1                     | 0     | 1     | 1                           | 1                             | 1                       |

| 0     | 1                     | 1     | 0     | 0                           | 0                             | 0                       |

| 0     | 1                     | 1     | 1     | 0                           | 1                             | 0                       |

| 1     | 0                     | 0     | 0     | 0                           | 1                             | 0                       |

| 1     | 0                     | 0     | 1     | 0                           | 0                             | 0                       |

| 1     | 0                     | 1     | 0     | 1                           | 1                             | 1                       |

| 1     | 0                     | 1     | 1     | 1                           | 0                             | 0                       |

| 1     | 1                     | 0     | 0     | 0                           | 0                             | 0                       |

| 1     | 1                     | 0     | 1     | 0                           | 1                             | 0                       |

| 1     | 1                     | 1     | 0     | 1                           | 0                             | 0                       |

| 1     | 1                     | 1     | 1     | 1                           | 1                             | 1                       |

Puisque  $f(x_0, x_1, y_0, y_1) = 1$  si  $x_0x_1 = y_0y_1$  donc ce circuit est un comparateur d'égalité de nombres binaires à deux bits.

2. Expression logique :  $S_1=B_1\oplus B_2,\ S_2=B_2\oplus B_3, S_3=B_3\oplus B_4, S_4=B_4.$  Table de vérité

| $B_4$ | $B_3$ | $\boldsymbol{\mathit{B}}_{2}$ | $B_1$ | $S_4$ | $S_3$ | $S_2$ | $S_1$ |

|-------|-------|-------------------------------|-------|-------|-------|-------|-------|

| 0     | 0     | 0                             | 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 0                             | 1     | 0     | 0     | 0     | 1     |

| 0     | 0     | 1                             | 0     | 0     | 0     | 1     | 1     |

| 0     | 0     | 1                             | 1     | 0     | 0     | 1     | 0     |

| 0     | 1     | 0                             | 0     | 0     | 1     | 1     | 0     |

| 0     | 1     | 0                             | 1     | 0     | 1     | 1     | 1     |

| 0     | 1     | 1                             | 0     | 0     | 1     | 0     | 1     |

| 0     | 1     | 1                             | 1     | 0     | 1     | 0     | 0     |

| 1     | 0     | 0                             | 0     | 1     | 1     | 0     | 0     |

| 1     | 0     | 0                             | 1     | 1     | 1     | 0     | 1     |

| 1     | 0     | 1                             | 0     | 1     | 1     | 1     | 1     |

| 1     | 0     | 1                             | 1     | 1     | 1     | 1     | 0     |

| 1     | 1     | 0                             | 0     | 1     | 0     | 1     | 0     |

| 1     | 1     | 0                             | 1     | 1     | 0     | 1     | 1     |

| 1     | 1     | 1                             | 0     | 1     | 0     | 0     | 1     |

| 1     | 1     | 1                             | 1     | 1     | 0     | 0     | 0     |

Ce circuit réalise la conversion en code de Gray d'un nombre binaire de quatre bits.

### Exercice 2

| В | C | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$S = \overline{C}.B + C.\overline{B} = C \oplus B.$$

## Exercice 3

1. Réalisation de la fonction f avec un MUX  $8 \rightarrow 1$ . 2. Réalisation de la fonction f avec un

MUX  $4 \rightarrow 1$ .

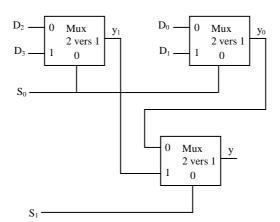

## **Exercice 4** Synthèse d'un MUX à 2 entrées

Symbole logique d'un MUX  $2 \rightarrow 1$

Ce MUX possède une ligne de sélection des données, puisqu'il est possible de sélectionner l'une ou l'autre des 2 lignes d'entrée de données avec seulement un bit. Soit, la table de vérité suivante :

| Entrée de sélection<br>S <sub>0</sub> | Entrée sélectionnée |

|---------------------------------------|---------------------|

| 0                                     | $D_0$               |

| 1                                     | $D_1$               |

La sortie des données est égale à  $D_0$  seulement si  $S_0 = 0$ :  $Y = D_0 \overline{S}_0$ .

La sortie des données est égale à  $D_1$  seulement si  $S_0 = 1$ :  $Y = D_1 S_0$ .

D'où la fonction de sortie :

$$Y = D_{0}\overline{S}_{0} + D_{1}.S_{0}..$$

Soit, le logigramme correspondant est :

# Exercice 5

Table de vérité

| а | b | С | x | у | z |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 |

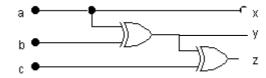

## Expressions logiques

$$x = a$$

$$y = a \oplus b$$

.

$$z = (a \oplus b) \oplus c$$

.

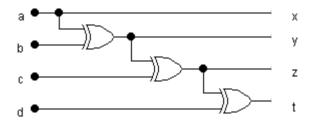

## 5. Logigramme si le code d'entrée est sur 4 bits.

Si le code d'entrée est sur 4 bits, il est facile, de déduire par récurrence que ses équations logiques sont :

$$x = a.$$

$$y = a \oplus b.$$

$$z = (a \oplus b) \oplus c.$$

$$t = \bigl(\bigl(a \oplus b\bigr) \oplus c\bigr) \oplus d.$$

Ainsi, le logigramme d'un transcodeur binaire réfléchi / binaire naturel est :

Planche d'Exercices N<sup>0</sup>2 Bascules et Bistables L1 – S2– MI -- 2019-2020

« ... Tu m'apprends que le Bien est impossible, je parie donc que je ferai du Bien : c'est encore la meilleure manière d'être seul.» Jean Paul Sartre.

#### **Exercice 1**

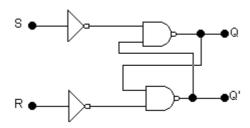

Construire le verrou RS en utilisant  $\overline{R}$ ,  $\overline{S}$  et les portes NAND.

#### Exercice 2

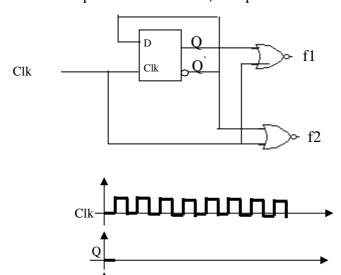

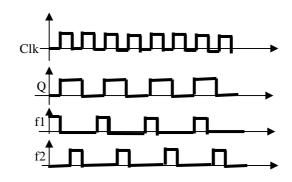

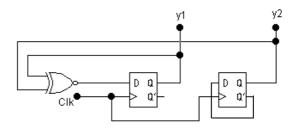

Soit le circuit séquentiel ci-dessous, compléter le chronogramme qui suive.

### **Exercice 3**

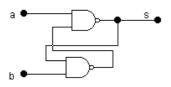

- 1. Donnez la table de vérité du montage ci-dessous :

- 2. Quelle fonction reconnaissez-vous?

#### **Exercice 4**

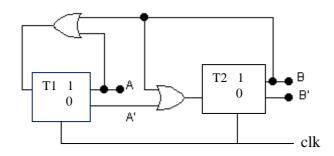

Soit le circuit séquentiel suivant :

Donner sa table de transition puis, Donner les équations caractéristiques de ce circuit.

# Corrigé : Série 2 : Bascules

## **Exercice 1**

# **Exercice 2**

# **Exercice 3**

1. table de vérité.

| а | b | S | S+ |

|---|---|---|----|

| 0 | 0 | 0 | X  |

| 0 | 0 | 1 | X  |

| 0 | 1 | 0 | 1  |

| 0 | 1 | 1 | 1  |

| 1 | 0 | 0 | 0  |

| 1 | 0 | 1 | 0  |

| 1 | 1 | 0 | 0  |

| 1 | 1 | 1 | 1  |

2. C'est la bascule SR avec R = a et S = b.

## **Exercice 4**

## 1. Table de transition

| Α | A' | В | T1 | T2 | A+ | B+ |

|---|----|---|----|----|----|----|

| 0 | 1  | 0 | 0  | 1  | 0  | 1  |

| 0 | 1  | 1 | 1  | 1  | 1  | 0  |

| 1 | 0  | 0 | 1  | 0  | 0  | 0  |

| 1 | 0  | 1 | 1  | 1  | 0  | 0  |

2. Equations caractéristiques du circuit

A+=T1.A' et B+=T2.B'.

## Planche d'Exercices N<sup>0</sup>3 Registres L1 – S2– MI -- 2019-2020

« la mémoire est l'avenir du passé.» Paul Valery.

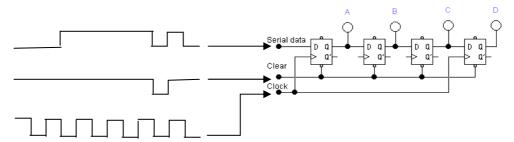

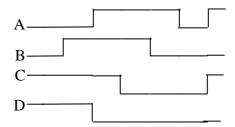

### **Exercice 1**

Tracer les signaux de sortie A, B, C et D après chaque impulsion de l'horloge.

## **Exercice 2**

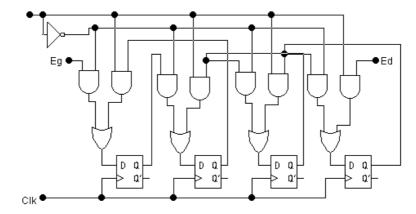

Réaliser, à base de bascules D, un registre à décalage à droite et à gauche 4 bits, selon un signal de sélection s tel que : s=0 décalage à droite s=1 décalage à gauche.

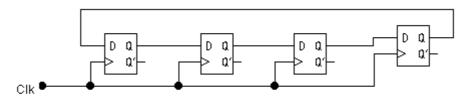

### **Exercice 3**

Analyser le circuit suivant :

Annexe : différents types de registres

| Entrée série / Sortie série     | Entrée parallèle / sortie série     |

|---------------------------------|-------------------------------------|

| Entrée Sortie                   | Entrée Sortie                       |

| Entrée série / sortie parallèle | Entrée parallèle / sortie parallèle |

| Entrée<br>Sortie                | Entrée<br>Sortie                    |

## Corrigé : Série 3 : Registres

#### **Exercice 1**

#### **Exercice 2**

Les équations caractéristiques d'un registre à décalage à droite, formé de 4 bascule D, à front montant sont :  $D_4=Q_3$ ,  $D_3=Q_2$ ,  $D_2=Q_1$ ,  $D_1=E_g$ .

Les équations caractéristiques d'un registre à décalage à gauche, formé de 4 bascule D, à front montant sont :  $D_1=Q_2$ ,  $D_2=Q_3$ ,  $D_3=Q_4$ ,  $D_4=Ed$

D'où, Les équations caractéristiques d'un registre à décalage à droite et à gauche, formé de 4 bascule D,à front montant sont :  $D_1=x'$ . Eg+x.  $Q_2$ ,  $D_2=x'$ .  $Q_1+x$ .  $Q_3$ ,  $D_3=x'$ .  $Q_2+x$ .  $Q_4$ ,  $D_4=x'$ .  $Q_3+x$ . Ed

**Exercice 3** Les équations d'entrée du système sont :  $D_1=Q_4$ ,  $D_2=Q_1$ ,  $D_3=Q_2$ ,  $D_4=Q_3$ . La table caractéristique du circuit est :

| $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $Q_1$ | Q2' | Q3' | Q <sub>4</sub> ' |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|-----|------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0   | 0   | 0                |

| 0     | 0     | 0     | 1     | 1     | 0     | 0     | 0     | 1     | 0   | 0   | 0                |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0   | 0   | 1                |

| 0     | 0     | 1     | 1     | 1     | 0     | 0     | 1     | 1     | 0   | 0   | 1                |

| 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0   | 1   | 0                |

| 0     | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 1     | 0   | 1   | 0                |

| 0     | 1     | 1     | 0     | 0     | 0     | 1     | 1     | 0     | 0   | 1   | 1                |

| 0     | 1     | 1     | 1     | 1     | 0     | 1     | 1     | 1     | 0   | 1   | 1                |

| 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1   | 0   | 0                |

| 1     | 0     | 0     | 1     | 1     | 1     | 0     | 0     | 1     | 1   | 0   | 0                |

| 1     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | 0     | 1   | 0   | 1                |

| 1     | 0     | 1     | 1     | 1     | 1     | 0     | 1     | 1     | 1   | 0   | 1                |

| 1     | 1     | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 1   | 1   | 0                |

| 1     | 1     | 0     | 1     | 1     | 1     | 1     | 0     | 1     | 1   | 1   | 0                |

| 1     | 1     | 1     | 0     | 0     | 1     | 1     | 1     | 0     | 1   | 1   | 1                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1   | 1   | 1                |

C'est un registre à décalage à droite sur 4 bits. En plus, il ya une rotation des bits. Donc, c'est un registre à décalage à droite avec rotation.

## Planche d'Exercices N<sup>0</sup>4 Mémoires L1 – S2– MI -- 2019-2020

« la mémoire est nécessaire pour toutes les operations de la raison.» Blaise Pascal.

#### Exercice 1

Quelles sont les différences entre des mémoires volatile, dynamique et statique?

#### Exercice 2

On considère une mémoire centrale de 2 Mbytes, où chaque byte est adressable séparément.

- 1. Calculer l'adresse, en octal, du sixième élément d'un tableau dont l'adresse du premier élément est 77<sub>8</sub>, et dont tous les éléments sont composés de 16 bits.

- 2. Calculer la taille de cette mémoire en l'exprimant en mots de 16 bits et en mots de 32 bits.

#### **Exercice 3**

Déterminer le nombre de ligne d'adresse pour une mémoire de capacité 64K\*8.

#### **Annexe**

1K (Kilo) = $10^3 \approx 2^{10} = 1024$  bits. 1M (Méga) = $10^6 \approx 2^{20} = 1048$  576 bits. 1G (Giga) = $10^9 \approx 2^{30} = 1073$  741 824 bits.

### **Corrigé : Série 4 : Mémoires**

#### **Exercice 1**

Une mémoire volatile est une mémoire qui perd son contenu lorsqu'elle n'est plus sous tension. Une mémoire dynamique est une mémoire volatile qui en plus doit être rafraichie plusieurs fois par seconde pour ne pas perdre son contenu, alors qu'une mémoire statique est aussi une mémoire volatile mais qui n'a pas besoin de rafraichissement.

#### Exercice 2

Mémoire centrale de 2 Mbytes.

Chaque élément est stocké sur 2 bytes , donc le sixième élément se trouve à l'adresse de départ + 10 bytes, ce qui donne  $77_8+12_8=111_8$  (63+10=73).

La taille de la mémoire est de 2 Mbytes ou de 1 Mmots de 16 bits, ou de 512 Kmots de 32 bits.

#### Exercice 3

Une mémoire de 64K\*8 est organisée en mots de 8 bits, et a une capacité de 64K octets. Soit n le nombre de lignes d'adresse, on a donc :  $64K=2^n$  d'où n=Ln (64\*1024)/Ln2=16.

## Planche d'Exercices N<sup>0</sup>5 Analyse et Synthèse de circuits séquentiels L1 – S2– MI -- 2019-2020

«Il réalisait parmi les hommes cette figure parfaite que le cercle réalise parmi les lignes géométriques. C'était un Zéro.» Victor Hugo.

#### Exercice 1

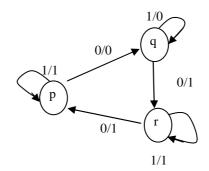

Soit M = (Q, U, Y, Init, R, S) une machine, où  $Q = \{p, q, r\}$  et  $U = Y = \{0, 1\}$ ; définie par les diagrammes de transition et de sortie suivants :

| R | 0 | 1 |

|---|---|---|

| p | q | p |

| q | r | q |

| r | р | r |

| S | 0 | 1 |

|---|---|---|

| p | 0 | 1 |

| q | 1 | 0 |

| r | 1 | 1 |

Décrire son graphe d'état.

#### Exercice 2

Soit un compteur, décrit par le graphe logique ci-dessous. Quelle est la séquence de comptage ? (les variables sont données dans l'ordre  $y_1y_2$ ).

$$a/0 \rightarrow 1 \rightarrow 2 \rightarrow 3$$

.  $b/0 \rightarrow 3 \rightarrow 2 \rightarrow 1$ .  $c/0 \rightarrow 2 \rightarrow 1 \rightarrow 3$ .  $d/0 \rightarrow 3 \rightarrow 1 \rightarrow 2$ .

#### Exercice 3

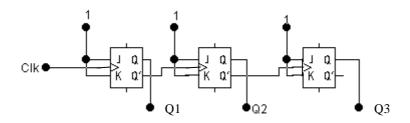

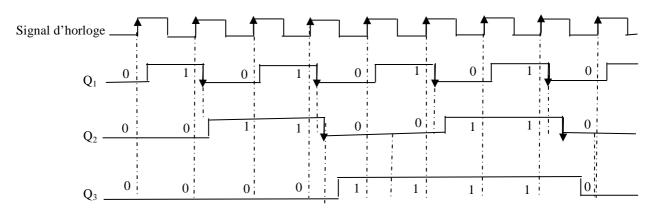

Soit le circuit de la figure ci-dessous, composé de bascule de type JK à front montant.

- 1. Décrire le comportement des différentes bascules de ce circuit.

- 2. Le circuit est-il synchrone ou asynchrone? Pourquoi?

- 3. Donner le chronogramme de fonctionnement de ce circuit.

- 4. En déduire la table des transitions après chaque impulsion d'horloge.

- 5. Quel est le travail effectuer par ce circuit.

#### **Exercice 4**

Faire la synthèse d'un compteur synchrone progressif modulo 5, formé de trois bascules type D à front descendant.

Faire la synthèse d'un compteur synchrone régressif modulo 7, formé de trois bascules type JK à front descendant.

### Corrigé : Série 5: Synthèse de circuits séquentiels

#### **Exercice 1**

#### Exercice 2

C'est la séquence b.

### Exercice 3

Décrivons le comportement de chaque bascule

Les équations de la bascule 1 sont :  $Q_1^+ = \overline{Q_1}$  car  $J_1 = K_1 = 1$ .

A chaque front montant de clk on a :  $Q_1^+ = \overline{Q_1}$ .

Les équations de la bascule 2 sont :  $Clk_2 = \overline{Q_1}$ ,  $Q_2^+ = \overline{Q_2}$  car  $J_2 = K_2 = 1$ .

A chaque front descendant de  $Q_1$  on a :  $Q_2^+ = \overline{Q_2}$ .

Les équations de la bascule 3 sont :  $Clk_3 = \overline{Q_2}$ .  $Q_3^+ = \overline{Q_3}$ . car  $J_3 = K_3 = 1$ .

A chaque front descendant de  $Q_2$  on a :  $Q_3^+ = \overline{Q_3}$ .

2. Le circuit est asynchrone car le signal d'horloge est appliqué seulement à la première bascule et l'état de chaque bascule est fonction des états des bascules précédentes.

3. Chronogramme du fonctionnement du circuit

#### 4. Table de transition

| $Q_3$ | $Q_2$ | $Q_1$ | $Q_3$ | $Q_2^+$ | $Q_1^+$ |

|-------|-------|-------|-------|---------|---------|

| 0     | 0     | 0     | 0     | 0       | 1       |

| 0     | 0     | 1     | 0     | 1       | 0       |

| 0     | 1     | 0     | 0     | 1       | 1       |

| 0     | 1     | 1     | 1     | 0       | 0       |

| 1     | 0     | 0     | 1     | 0       | 1       |

| 1     | 0     | 1     | 1     | 1       | 0       |

| 1     | 1     | 0     | 1     | 1       | 1       |

| 1     | 1     | 1     | 0     | 0       | 0       |

5. C'est un compteur binaire asynchrone progressif modulo 8.

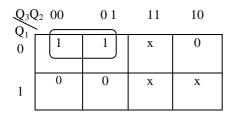

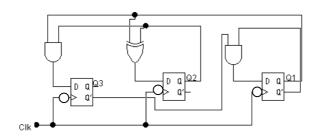

## **Exercice 4**

1. Faisons la synthèse d'un compteur synchrone progressif modulo 5 (compte de 0 à 4), formé de trois bascules type D à front descendant.

| $Q_3$ | $Q_2$ | $Q_1$ | $Q_3^+$ | $Q_2^+$ | $Q_1^+$ | $D_3$ | $D_2$ | $D_1$ |

|-------|-------|-------|---------|---------|---------|-------|-------|-------|

| 0     | 0     | 0     | 0       | 0       | 1       | 0     | 0     | 1     |

| 0     | 0     | 1     | 0       | 1       | 0       | 0     | 1     | 0     |

| 0     | 1     | 0     | 0       | 1       | 1       | 0     | 1     | 1     |

| 0     | 1     | 1     | 1       | 0       | 0       | 1     | 0     | 0     |

| 1     | 0     | 0     | 0       | 0       | 0       | 0     | 0     | 0     |

| 1     | 0     | 1     | X       | X       | X       | X     | X     | X     |

| 1     | 1     | 0     | X       | X       | X       | X     | X     | X     |

| 1     | 1     | 1     | X       | X       | X       | X     | X     | X     |

Les équations logiques :

| $Q_3$ | Q <sub>2</sub> 00 | 0 1 | 11            | 10 |

|-------|-------------------|-----|---------------|----|

| 0     | 0                 | 0   | X             | 0  |

|       |                   |     | $\rightarrow$ |    |

| 1     | 0                 |     | X             | X  |

| $Q_3$ | $Q_2 00$ | 0 1 | 11 | 10 |

|-------|----------|-----|----|----|

| $Q_1$ | 0        | 1   | x  | 0  |

|       |          |     |    |    |

| 1     |          | 0   | X  | X  |

$$D_{\scriptscriptstyle 3} = Q_{\scriptscriptstyle 2} Q_{\scriptscriptstyle 1}$$

$$D_{\scriptscriptstyle 2} = Q_{\scriptscriptstyle 1} \oplus Q_{\scriptscriptstyle 2}$$

$$D_{\scriptscriptstyle 1} = \overline{Q_{\scriptscriptstyle 3}}.\overline{Q_{\scriptscriptstyle 1}}$$

Schéma logique

Compteur synchrone progressif modulo 5 formé de bascule type D

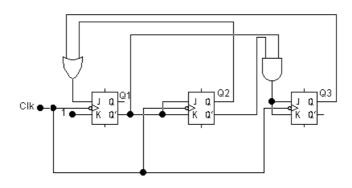

2. Faisons la synthèse d'un compteur synchrone régressif modulo 7 (compte de 0 à 6), formé de trois bascules type JK à front descendant.

| $Q_3$ | $Q_2$ | $Q_1$ | $Q_3^+$ | $Q_2^+$ | $Q_1^+$ | $J_3$ | $K_3$ | $J_2$ | $K_2$ | $J_1$ | $\mathbf{K}_{1}$ |

|-------|-------|-------|---------|---------|---------|-------|-------|-------|-------|-------|------------------|

| 1     | 1     | 1     | X       | X       | X       | X     | X     | X     | X     | X     | X                |

| 1     | 1     | 0     | 1       | 0       | 1       | X     | 0     | X     | 1     | 1     | X                |

| 1     | 0     | 1     | 1       | 0       | 0       | X     | 0     | 0     | X     | X     | 1                |

| 1     | 0     | 0     | 0       | 1       | 1       | X     | 1     | 1     | X     | 1     | X                |

| 0     | 1     | 1     | 0       | 1       | 0       | 0     | X     | X     | 0     | X     | 1                |

| 0     | 1     | 0     | 0       | 0       | 1       | 0     | X     | X     | 1     | 1     | X                |

| 0     | 0     | 1     | 0       | 0       | 0       | 0     | X     | 0     | X     | X     | 1                |

| 0     | 0     | 0     | 1       | 1       | 0       | 1     | X     | 1     | X     | 0     | X                |

# Les équations logiques :

| $Q_3$ | $Q_2 = 00$ | 0 1 | 11 | 10_ |

|-------|------------|-----|----|-----|

| $Q_1$ | 1          | 0   | X  | (x  |

| 1     | 0          | 0   | Х  | Х   |

| $Q_3$ | $Q_2 = 00$ | 0 1 | 11 | 10 |

|-------|------------|-----|----|----|

| 0     | x          | X   | 0  | 1  |

| 1     | Х          | X   | X  | 0  |

$$J_3 = \overline{Q_2} \overline{Q_1}.$$

| $Q_3$ | $Q_2 = 00$ | 0 1 | 11 | 10 |

|-------|------------|-----|----|----|

| $Q_1$ | 1          | X   | X  | 1  |

| 1     | 0          | X   | X  | 0  |

$$J_{2}=\overline{Q_{1}}.$$

| Q3(   | $Q_2 = 00$ | 0.1 |   | 10 |

|-------|------------|-----|---|----|

| $Q_1$ | 0          | 1   | 1 | 1  |

| 1     | Х          | X   | X | х  |

$$J_{1} = Q_{2} + Q_{3}.$$

$K_{_3}=\overline{Q_{_2}.Q_{_1}}.$

| $Q_3$ | $Q_2 = 00$ | 0 1 | 11 | 10 |

|-------|------------|-----|----|----|

| $Q_1$ | X          | 1   | 1  | х  |

| 1     | Х          | 0   | X  | X  |

$$K_2 = \overline{Q_1}$$

.

| $Q_3$ | $Q_2$ | 00 | 0 1 | 11 | 10 |  |

|-------|-------|----|-----|----|----|--|

| $Q_1$ |       | X  | X   | X  | x  |  |

| O     |       | 1  | 1   |    | 1  |  |

| 1     |       | 1  | 1   | X  |    |  |

| -     |       | _  |     |    |    |  |

$K_1 = 1$ .

## Schéma logique

Compteur synchrone régressif modulo 7 formé de bascule type JK