# République Algérienne Démocratique et Populaire Ministère de l'enseignement supérieur et de la recherche scientifique

Université Abou Bekr Belkaid - Tlemcen Faculté de technologie. Département GEE.

.....

# Polycopié

# Cours **Logique et Calculateur Numérique**

Licence Electronique

Par MOULAI KHATIR Ahmed Nassim Année universitaire 2016-2017

# Cours **Logique et Calculateur Numérique**

# **Programme:**

Chap I : Système de numération et codage.

Chap II : Algèbre de Boole et fonction booléennes.Chap III : Simplification des fonctions logiques.

Chap IV : Analyse et synthèse des circuits logiques combinatoire.

Chap V : Analyse et synthèse des circuits logiques séquentiels.

# Chapitre I : Système de numération et codage

.....

#### **Introduction:**

Pour la mesure des grandeurs physiques dans la plus part des domaines (Température, Vitesse, Voltage...), on peut représenter précisément leurs valeurs sous deux formes différentes :

- 1- Représentation analogique.

- 2- Représentation numérique.

<u>a - Représentation analogique</u>: Dans cette représentation on fait correspondre à une grandeur physique une autre grandeur physique qui lui est proportionnelle.

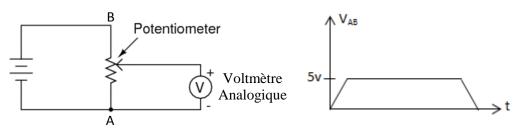

#### Ex : Soit le circuit suivant :

Figure I.1: Mesure Analogique

Lorsqu'on fait déplacer le curseur du potentiomètre de bas en haut, la tension entre les points A et B croit progressivement de 0V jusqu'à 5V. Si le curseur se déplace de haut en bas, la tension décroit peu à peu de 5V jusqu'à attendre 0V.

Dans ce cas la valeur de la tension  $V_{AB}$  est donnée par la position de l'aiguille sur le cadran du voltmètre (donc on a fait correspondre à la grandeur « tension » une autre grandeur physique qui est la position de l'égaille « l'angle  $\theta$  »

Donc un élément analogique est un dispositif dont la sortie varie d'une manière continue avec l'entrée

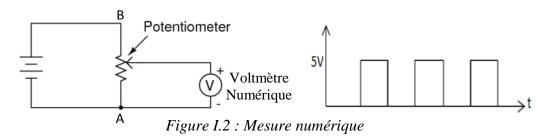

$\underline{b}$ - Représentation Numérique (Digitale): Prenons l'exemple précèdent; cette foi si en remplace le voltmètre analogique par un voltmètre numérique. Dans ce cas on fait correspondre à la tension  $V_{AB}$  un nombre.

En déplaçant le curseur, on peut lire sur le cadran du voltmètre les chiffres 0, 1, 2, 3, 4 ...

On remarque que la sortie varie de façon discrète (discontinue).

Les circuits numériques digitaux ne fonctionnent qu'à l'aide des signaux discrets.

L'afficheur utilisé ici est constitué de quatre segments qui ne peuvent être allumés qu'à l'aide d'un signal carré

Ces circuits n'admettent que deux valeurs significatives :

- Une tension haute (de niveau haut) désignée par la valeur 1 (logique 1 ou état 1).

- Une tension basse (de niveau bas) désignée par la valeur 0 (logique 0 ou état 0).

## Pourquoi utiliser des circuits digitaux :

Les systèmes digitaux sont nécessaires quand l'information doit être utilisée dans d'autres calculs ou affichage (en nombres et/ou en lettres).

## Les avantages des circuits digitaux :

- 1- L'information peut être stockée

- 2- Les données peuvent êtres utilisées pour des calcules précis

- 3- La possibilité de programmation (rendre un système intelligent) ↔ compatibilité avec les micro-ordinateurs.

- 4- Les circuits digitaux sont disponibles sur des circuits intégrés pas chers.

#### Les limites :

- 1- La majorité des phénomènes réels sont de nature analogique.

- 2- Le traitement analogique est généralement plus simple et plus rapide.

# I- Systèmes de numération :

L'ensemble des outils informatiques sont basés sur les mêmes principes de calcul (loi de tout ou rien). Les calculs habituels sont effectués dans le système de numération décimal, par contre le calculateur électronique ne peut pas utiliser ce système car le circuit électronique ne permet pas de distinguer 10 états. Le système de numération binaire ne comportera que 2 états 0 et 1.

# I.1- la valeur du digit (chiffre):

#### Considérons le nombre 528 :

Le digit 5 représente 500 à cause de sa 3eme position à gauche du point décimal.

Le digit 2 représente 20 à cause de sa 2eme position à gauche du point décimal.

Le digit 8 représente 8 à cause de sa 1ere position à gauche du point décimal.

Le nombre total représente donc 500+20+8

- On remarque que chaque digit a un poids en fonction de sa position.

- Ceci est valable pour tous les systèmes de numérotation qui existent (pas uniquement pour le système décimal).

Tout nombre  $N_b$  qui comprend n chiffres donné en base b peut être exprimé comme la somme de ses coefficients pondérés.

$$\begin{split} N_b &= x_n x_{n\text{-}1} x_{n\text{-}2} \dots \ x \\ N_b &= x_n b^n + x_{n\text{-}1} b^{n\text{-}1} + x_{n\text{-}2} b^{n\text{-}2} + \dots + x_0 b^0 \\ N_b &= \sum_{i=0}^n x_i b^i \end{split}$$

Ex.

$$528=5.10^2+2.10^1+8.10^0$$

# I.2- Système décimal :

Le système décimal est celui dans lequel nous avons le plus l'habitude d'écrire. Chaque chiffre peut avoir 10 valeurs différentes : 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, de ce fait, le système décimal a pour base 10.

Développement en polynôme d'un nombre dans le système décimal

• Soit le nombre 1978, ce nombre peut être écrit sous la forme suivante :

$$1978 = 1000 + 900 + 70 + 8$$

$$1978 = 1*1000 + 9*100 + 7*10 + 8*1$$

$$1978 = 1*10^{3} + 9*10^{2} + 7*10^{1} + 8*10^{0}$$

Cette forma s'appelle la forme polynomiale

Un nombre réel peut être écrit aussi sous la forme polynomiale  $1978, 265=1*10^3 + 9*10^2 + 7*10^1 + 8*10^0 + 2*10^{-1} + 6*10^{-2} + 5*10^{-3}$ .

Cependant il est possible d'imaginer d'autres systèmes de nombres ayant comme base un nombre entier différent.

## I.3- Système octal:

Le système octal utilise un système de numération ayant comme base 8 (octal => latin : octo = huit). Dans ce système nous n'aurons plus 10 symboles mais 8 seulement : 0, 1, 2, 3, 4, 5, 6, 7

Ainsi, un nombre exprimé en base 8 pourra se présenter de la manière suivante :  $(745)_8$ . Cette base obéira aux mêmes règles que la base 10, vue précédemment, ainsi on peut décomposer  $(745)_8$  de la façon suivante :

$$(745)_8 = 7 \times 8^2 + 4 \times 8^1 + 5 \times 8^0$$

$(745)_8 = 7 \times 64 + 4 \times 8 + 5 \times 1$

$(745)_8 = 448 + 32 + 5$

Nous venons de voir que :  $(745)_8 = (485)_{10}$ .

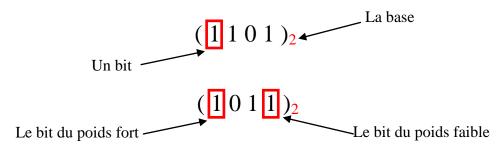

# I.4- Système binaire :

Dans le système binaire, chaque chiffre peut avoir 2 valeurs différentes : 0, 1. De ce fait, le système a pour base 2.

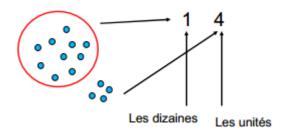

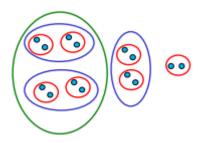

#### Exemple illustratif:

Supposons qu'on a 14 jetons, si on forme des groupes de 10 jetons. On va obtenir 1 seul groupe et il reste 4 jetons.

- . Maintenant on va former des groupes de 2 jetons (on obtient 7 groupes)

- . Par la suite on va regrouper les 7 groupes 2 à 2 (on obtient 3 groupes).

- . On va regrouper ces derniers aussi 2 à 2 (on obtient 1 seul groupe)

- . Le schéma illustre le principe :

Nombre de jetons qui restent en dehors des groupes : 0

Nombre de groupes qui contiennent 2 jetons : 1

Nombre de groupes qui contiennent 2 groupes de 2 jetons : 1

Nombre de groupes qui contiennent des groupes de 2 groupes de 4 jetons : 1

Si on regroupe les différents chiffres on obtient : 1110

1110 est la représentation de 14 dans la base 2

Figure I.3: Poids d'un nombre binaire

# Comptage en binaire :

Sur un seul bit: 0, 1

Sur deux bits : 4 combinaisons =  $2^2$

| Binaire | Décimal |

|---------|---------|

| 00      | 0       |

| 01      | 1       |

| 10      | 2       |

| 11      | 3       |

Sur trois bits : 8 combinaisons =  $2^3$

| Binaire | Décimal |

|---------|---------|

| 000     | 0       |

| 001     | 1       |

| 010     | 2       |

| 011     | 3       |

| 100     | 4       |

| 101     | 5       |

| 110     | 6       |

| 111     | 7       |

Table I.1 : Comptage en binaire

# I.5- Système hexadécimale :

Le système hexadécimal utilise les 16 symboles suivant :

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F: De ce fait, le système a pour base 16.

| Base 10 | Base 16 | Base 2 |

|---------|---------|--------|

| 0       | 0       | 0      |

| 1       | 1       | 1      |

| 2       | 2       | 10     |

| 3       | 3       | 11     |

| 4       | 4       | 100    |

| 5       | 5       | 101    |

| 6       | 6       | 110    |

| 7       | 7       | 111    |

| 8       | 8       | 1000   |

| 9       | 9       | 1001   |

| 10      | A       | 1010   |

| 11      | В       | 1011   |

| 12      | С       | 1100   |

| 13      | D       | 1101   |

| 14      | Е       | 1110   |

| 15      | F       | 1111   |

Table I.2 : Correspondance Décimal-Hexadécimal-Binaire

Un nombre exprimé en base 16 pourra se présenter de la manière suivante :  $(5AF)_{16}$  La correspondance entre base 2, base 10 et base 16 est indiquée dans le tableau I.2 :

Le nombre (5AF)<sub>16</sub> peut se décomposer comme suit :

$$(5AF)_{16} = 5 \times 16^2 + A \times 16^1 + F \times 16^0$$

En remplaçant A et F par leur équivalent en base 10, on obtient :

$$(5AF)_{16} = 5 \times 16^2 + 10 \times 16^1 + 15 \times 16^0$$

$$(5AF)_{16} = 5 \times 256 + 10 \times 16 + 15 \times 1$$

donc =

$$(5AF)_{16} = (1455)_{10}$$

## **II- Transcodage:**

En électronique digital presque tous les circuits digitaux (calculateurs, ordinateurs) ne comprennent que les nombres binaires, mais les gens ne comprennent que les nombres décimaux. Donc nous devons traduire ou convertir du décimal au binaire et du binaire au décimal.

## II.1. Conversion binaire-décimal:

Soit le nombre binaire (110011)<sub>2</sub>

$$N=1.2^{0}+1.2^{1}+0.2^{2}+0.2^{3}+1.4^{2}+1.2^{5}$$

La conversion du nombre binaire N dans son équivalent décimal est immédiate, Elle découle du calcul effectué dans la base 10

$$N=1+2+16+32=(51)_{10}$$

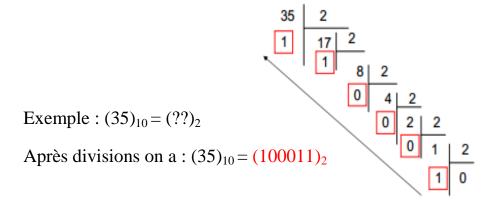

#### II.2. Conversion décimal - binaire :

Cas d'un nombre Entier :

Figure I.4: Devisions successives par 2

**1**<sup>er</sup> **Méthode :** La conversion d'un nombre décimal N dans son équivalent binaire peut être effectuée par une succession de devisions par 2 jusqu'à l'obtention d'un quotient nul (*Fig. I.4*) et prendre le reste des divisions dans l'ordre inverse.

#### 2<sup>eme</sup> Méthode: Soustraction successive

La méthode consiste à retrancher du nombre  $N_{10}$  la plus grande puissance entière de contenue dans  $N_{10}$ . On considère ensuite le reste, et on recommence l'opération jusqu'à l'obtention de 0

#### Cas d'un nombre réel :

Un nombre réel est constitué de deux parties : la partie entière et la partie fractionnelle.

- La partie entière est transformée en effectuant des divisions successives.

- La partie fractionnelle est transformée en effectuant des multiplications successives par 2.

# <u>Exemple</u>

$$35,625 = (?)_2$$

$0,625 * 2 = 1,25$

Partie Entière :  $35 = (100011)_2$   $0,25 * 2 = 0,5$

Partie Fractionnelle :  $0,625 = (?)_2$   $0,5 * 2 = 1,0$

$$(0,625) = (0,101)_{2}$$

Donc:  $35,625 = (100011,101)_{2}$

$$\underbrace{Exemple \ 2}_{(0,4)10 = (??)_{2}}$$

$$0,4 * 2 = 0,8$$

$$0,8 * 2 = 1,6$$

$$0,6 * 2 = 1,2$$

$$0,2 * 2 = 0,4$$

$$(0,4) = (0,0110)_{2}$$

#### Remarque

Le nombre de bits après la virgule détermine la précision de la conversion

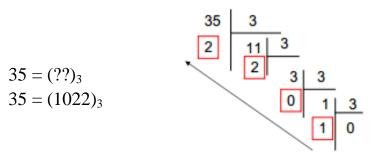

#### II.3. Conversion du décimal à une base X :

La conversion se fait en prenant les restes des divisions successives sur la base X dans le sens inverse.

#### <u>Exemple</u>

Figure I.5 : Devisions successives par 3

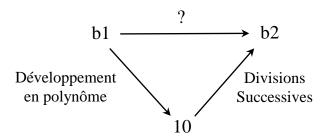

#### II.4. Conversion d'une base b1 à une base b2 :

- Il n'existe pas de méthode pour passer d'une base b1 à une autre base b2 directement.

- L'idée est de convertir le nombre de la base b1 à la base 10 , en suit convertir le résultat de la base 10 à la base b2 .

Exemple

$$(34)_5 = (?)_7$$

$(34)_5 = 3*5^1 + 4*5^0 = 15 + 4 = (19)_{10} = (19)_{10} = (?)_7$

$$(19)_{10} = (25)_7$$

$$(34)_5 = (25)_7$$

## II.5. Conversion: binaire – octal

L'avantage que présentent les systèmes octal et hexadécimal est la facilité de la conversion directe au système binaire.

Pour passer d'un nombre écrit en binaire a son équivalent octal, il faut diviser ce nombre en groupement de 3 bits commençant du point décimal (point binaire), et remplacer chaque groupement par son équivalent en octal.

| Exemple:                                                                               |

|----------------------------------------------------------------------------------------|

| $(345)_8 = (\underline{011} \ \underline{100} \ \underline{101})_2$                    |

| $(65,76)_8 = (\underline{110} \ \underline{101}, \underline{111} \ \underline{110})_2$ |

| $(35,34)_8 = (\underline{011} \ \underline{101}, \underline{011} \ \underline{100})_2$ |

| Octal | Binaire |

|-------|---------|

| 0     | 000     |

| 1     | 001     |

| 2     | 010     |

| 3     | 011     |

| 4     | 100     |

| 5     | 101     |

| 6     | 110     |

| 7     | 111     |

Remarque : Le remplacement se fait de droit à gauche pour la partie entière et de gauche à droite pour la partie fractionnelle.

#### II.6. Conversion : octal – binaire :

Pour passer du système octal au système binaire, il suffit d'inverser le processus i.e. écrire chaque chiffre (digit) en octal en son équivalent binaire sur 3 bits.

Exemple: soit à convertir le nombre octal (254)8

Octal: 2 5 4

Binaire: 010 101 100 =  $(10101100)_2$

Ou tout simplement passer par la base 10 en suite effectuer des divisions successives par 2

#### II.7. Conversion hexadécimal – binaire :

En Hexa chaque symbole de la base s'écrit sur 4 bits

L'idée de base est de replacer chaque symbole par sa valeur en binaire sur 4 bits (faire des éclatements sur 4 bits).

## **Exemple**

$(345B)_{16} = (\underline{0011} \ \underline{0100} \ \underline{0101} \ \underline{1011})_2$  $(AB3,4F6)_{16} = (\underline{1010} \ \underline{1011} \ \underline{0011}, \ \underline{0100} \ \underline{1111} \ \underline{0110})_2$

## II.8. Conversion binaire – hexadécimal:

L'idée de base est de faire des regroupements de 4 bits à partir du poids faible. Par la suite remplacer chaque regroupement par la valeur Hexa correspondante.

#### Exemple

```

(1100101010110)_2 = (\underline{0011} \ \underline{0010} \ \underline{1010} \ \underline{0110})_2 = (32A6)_{16}

(110010100,10101)_2 = (\underline{0001} \ \underline{1001} \ \underline{0100}, \underline{1010} \ \underline{1000})_2 = (194,A8)_{16}

```

# III - Opérations arithmétiques en binaire :

#### III.1. Addition:

Tableau d'addition:

| 0 | + | 0 = | 0 |                   |

|---|---|-----|---|-------------------|

| 0 | + | 1 = | 1 |                   |

| 1 | + | 0 = | 1 |                   |

| 1 | + | 1 = | 0 | Avec retenue de 1 |

#### **Exemple**

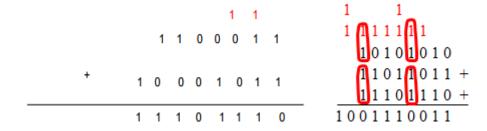

Figure I.6: Addition Binaire

# **III.2. Soustraction:**

Tableau de soustraction:

| 0 | - | 0 = 0 |                 |

|---|---|-------|-----------------|

| 0 | - | 1 = 1 | Avec retenue de |

| 1 | - | 0 = 1 |                 |

| 1 | - | 1 = 0 |                 |

Ex:

| 1         | 11 | 10 | 10 | 0 | 1  | 10 | <b>10</b> | 10 | 1 | 1  | 10 |

|-----------|----|----|----|---|----|----|-----------|----|---|----|----|

| <u>10</u> | 11 | 10 | 1  | 0 | 10 | 11 | 11        | 1  | 0 | 10 | 1  |

| 0         | 1  | 1  | 1  | 0 | 0  | 0  | 0         | 1  | 1 | 0  | 1  |

1

Figure I.7: Soustraction Binaire

# III.3. Multiplication:

Tableau de multiplication:

| $0 \times 0 = 0$ |  |

|------------------|--|

| $1 \times 0 = 0$ |  |

| 0 X 1 = 0        |  |

| 1 X 1 = 1        |  |

|                 |     |   |   |   |   | 1 | U  | U | Ι, | U | 1 | 1 |

|-----------------|-----|---|---|---|---|---|----|---|----|---|---|---|

| 1 0 1 1         |     |   |   |   | 1 | 0 | 1  | 0 | 0, | 1 | 1 |   |

| 1 1 0 1         |     |   |   |   |   | 1 | 0  | 0 | 1  | 0 | 1 | 1 |

| 1 0 1 1         |     |   |   |   | 1 | 0 | 0  | 1 | 0  | 1 | 1 | - |

| 1011            |     | 1 | 0 | 0 | 1 | 0 | 1  | 1 |    |   |   | - |

| 1011            | 10  | 0 | 1 | 0 | 1 | 1 | -  | - | -  | - |   | - |

| 1 0 0 0 1 1 1 1 | 1 1 | 0 | 0 | 0 | 0 | 1 | 0, | 1 | 0  | 0 | 0 | 1 |

Figure I.8: Multiplication Binaire

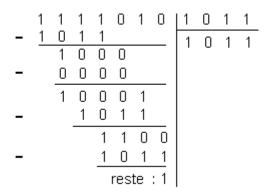

# **III.4. Division:**

Tableau de division:

| 0:0= indéterminé  |

|-------------------|

| 0:1=0             |

| 1:0 = indeterminé |

| 1:1=1             |

La division binaire s'effectue à l'aide de soustractions et de décalages, comme la division décimale, sauf que les digits du quotient ne peuvent être que 1 ou 0. Le bit du quotient est 1 si on peut soustraire le diviseur, sinon il est 0

Figure I.9: Division Binaire

## IV. Les codes Binaires

Pour des besoins de transmission d'informations un nombre important de codes a été créé :

## IV.1. Le code complément à deux

Le complément à deux est une représentation binaire des entiers relatifs qui permet d'effectuer les opérations arithmétiques usuelles naturellement.

Dans une telle écriture on utilise le bit de poids fort (bit le plus à gauche) du nombre pour contenir la représentation de son signe (le zéro étant considéré comme positif et le 1 comme négatif).

La première idée est de marquer le signe du nombre de façon simple : le signe puis la représentation de sa valeur absolue.

Ainsi sur 8 bits y compris le bit de signe :

| Bit se signe | Données | Décimal |  |

|--------------|---------|---------|--|

| 0            | 0000010 | +2      |  |

| 1            | 0000010 | -2      |  |

Malheureusement cette représentation possède deux inconvénients.

- Le nombre zéro (0) possède deux représentations: 0 0000000 et 1 0000000 sont respectivement égaux à 0 et -0.

- L'autre inconvénient (majeur) est que cette représentation n'est pas compatible avec l'addition usuelle.

Ainsi:

Pour la résolution de ce problème on utilise la notation en complément à deux. Les nombres positifs sont représentés comme attendu avec un bit de signe à 0 Les nombres négatifs sont obtenus de la manière suivante :

- On complémente à 1 les bits de l'écriture binaire de sa valeur absolue (Inversion de tout les bits).

- On ajoute 1 au résultat trouvé.

Les deux inconvénients précédents disparaissent alors.

$\mathbf{E}\mathbf{x}$

Pour coder (-4):

• On prend le nombre positif + 4 : 0 0000100

• On inverse les bits: 1 1111011

• On ajoute 1 : 1 1111100 correspond à – 4 en Complément à 2

Le bit de signe est automatiquement mis à 1 par l'opération d'inversion.

On peut vérifier que cette fois l'opération 3 + (-4) se fait sans erreur :

$$0\ 0000011 + 1\ 11111100 = 1\ 11111111$$

Le complément à deux de 1 1111111 est 0 0000001 soit 1 en décimal, donc 1 1111111 = (-1) en décimal.

Le résultat de l'addition usuelle de nombres représentés en complément à deux est le codage en complément à deux du résultat de l'addition des nombres.

## IV.2. Le code binaire naturel (Base 2) ou code 1248 :

| Décimal | Binaire |      |  |  |

|---------|---------|------|--|--|

| 0       | 0       | 0000 |  |  |

| 1       | 1       | 0001 |  |  |

| 2       | 10      | 0010 |  |  |

| 3       | 11      | 0011 |  |  |

| 4       | 100     | 0100 |  |  |

| 5       | 101     | 0101 |  |  |

| 6       | 110     | 0110 |  |  |

| 7       | 111     | 0111 |  |  |

| 8       | 1000    | 1000 |  |  |

| 9       | 1001    |      |  |  |

| 10      | 1010    |      |  |  |

| 11      | 1011    |      |  |  |

| 12      | 1100    |      |  |  |

| 13      | 1101    |      |  |  |

| 14      | 1110    |      |  |  |

| 15      | 1111    |      |  |  |

Table I.3 : Code Binaire Naturel

# IV. 3. Le Code Binaire Réfléchi (Code Gray):

Si on utilise le code binaire naturel pour effectuer un montage en risque d'avoir un problème en comptage avec les chiffres qui changes en même temps, La solution est d'utiliser le code réfléchi (Gray).

| Décimal | Binaire Gray |

|---------|--------------|

| 0       | 0000         |

| 1       | 0001         |

| 2       | 0011         |

| 3       | 0010         |

| 4       | 0110         |

| 5       | 0111         |

| 6       | 0101         |

| 7       | 0100         |

| 8       | 1100         |

| 9       | 1101         |

| 10      | 1111         |

| 11      | 1110         |

| 12      | 1010         |

| 13      | 1011         |

| 14      | 1001         |

| 15      | 1000         |

Table I.4 : Code Binaire Réfléchi

# IV. 4. Le Code BCD (Binary Code Decimal):

C'est la traduction en binaire de chaque chiffre décimal.

Chaque chiffre est exprimé séparément par un demi-octet (quatre bits).

| Décimal | Binaire Gray |

|---------|--------------|

| 0       | 0000         |

| 1       | 0001         |

| 2       | 0010         |

| 3       | 0011         |

| 4       | 0100         |

| 5       | 0101         |

| 6       | 0110         |

| 7       | 0111         |

| 8       | 1000         |

| 9       | 1001         |

|         |              |

Table I.5 : Code Binaire Décimal (BCD)

# IV. 5. Code avec Parité

C'est un code binaire pour le quel on rajoute un bit de parité pour savoir si la transmission s'est bien effectuée sans erreurs. On a deux possibilités de parité :

## Parité paire :

Dans le cas de la parité paire on compte le nombre de 1 contenu dans le nombre y compris le bit de parité, si ce nombre est paire on ajoute un 0 si non on ajoute un 1 comme bit de parité.

```

108_{10} = (01101100)_2= (001101100)_{2PP}100_{10} = (01100100)_2= (101101100)_{2PP}

```

## Parité impaire :

Dans le cas de la parité paire on compte le nombre de 1 contenu dans le nombre y compris le bit de parité, si ce nombre est impaire on ajoute un 0 si non on ajoute un 1 comme bit de parité.

```

108_{10} = (01101100)_{2}

= (101101100)_{2PI}

100_{10} = (01100100)_{2}

= (001101100)_{2PI}

```

# Chapitre II : Algèbre de Boole et fonction booléennes.

\_\_\_\_\_

#### **Introduction:**

Les circuits électroniques sont classés en deux grandes catégories :

Les circuits digitaux (numériques) et les circuits analogiques

Les circuits analogiques ont une amplitude variable continuellement, par contre un circuit digital est un circuit présentant un signal qui n'admet que deux niveaux (Ex +5V et 0V) équivalent au niveaux 1 et 0.

Un interrupteur est par exemple un circuit digital

# I. Algèbre de Boole et opérateurs logiques

En électronique numérique le jeu consiste à produire des sorties numériques (fonction logiques) a partir d'entrées numériques (variables logiques).

#### I.1. Définitions

L'algèbre de Boole est l'ensemble B={0,1} muni de trois lois élémentaires.

- Deux lois de composition : "ou" noté "x+y" (loi d'addition logique et "ET" noté "x.y" (loi de multiplication logique).

- Une loi de complémentation (négation) "Non" noté  $\overline{X}$

Avec X et Y sont deux éléments de l'ensemble B.

Ces lois peuvent être réalisées à partir d'un groupe d'opérations élémentaires appelées portes logiques (opérateurs logiques).

# I.2. Opérateurs logiques

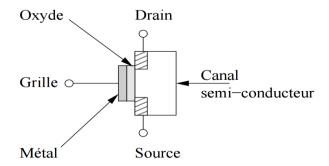

Chaque opérateur est représenté par un symbole, et sa fonction par une table de vérité. Ces opérateurs (portes logiques) sont conçus actuellement à base de Transistor qui est l'élément qui présente la brique de construction des circuits électroniques comme les puces, les microprocesseurs ... La technologie actuellement utilisée pour fabriquer ces portes est la technologie MOS (Metal-Oxide-Semiconductor). Il existe deux types de transistors MOS : les transistors de type n et les transistors de type p.

Figure II.1: Le transistor MOS

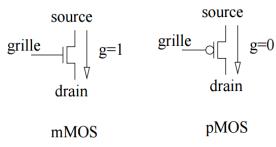

- Pour un n-MOS : Si la grille est mise à une tension positive, la source et le drain sont connectés. Si au contraire, la grille est mise à une tension de 0V, le circuit entre la source et le drain est ouvert.

- Pour un p-MOS c'est l'inverse : Le drain et la source sont connectés lorsque la tension appliquée à la grille est 0V

Un tel transistor (*Fig.II.1*) est composé de trois broches appelées drain, grille et source. Les rôles du drain et la source sont presque symétriques et interchangeables.

Le fonctionnement de ce transistor est semblable à un interrupteur électrique entre la source et le drain commandé par la

Figure. II.2: Les types nMOS et pMOS

Les micro-processeurs actuels utilisent des transistors des deux types. On parle alors de technologie CMOS (Complementary Metal-Oxide-Semiconductor).

Cette technologie (*Fig.II.3*) utilise les deux types du transistor (n-MOS et p-MOS), Si on applique un niveau haut à l'entrée, le transistor N est passant et le P est bloqué. La sortie est donc à l'état bas. Inversement, si on applique un état bas à l'entrée, le transistor N est bloqué et le P est passant. Donc la sortie est à l'état haut. Ce mécanisme présente une fonction d'inversion. Qui forme la porte de négation

Figure. II. 3: L'inverseur CMOS

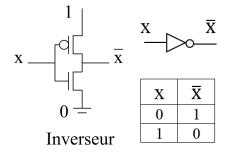

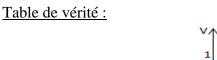

# I.1. La Porte Non (porte inverse)

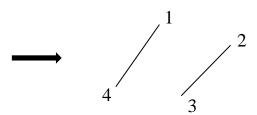

C'est une porte à une seule entrée, la variable de sortie est l'inverse de l'entrée. Symbole:

| Α | Ā |

|---|---|

| 0 | 1 |

| 1 | 0 |

Figure. II. 4: Diagramme temporel d'une porte "Non"

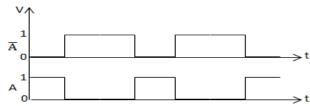

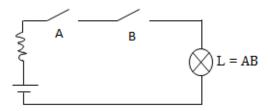

La sortie est égale à 1 si et seulement si l'entrée est égale à 0 et réciproquement. <u>Exemple</u>

La lampe ne s'allume (L=1) que si A (l'interrupteur) est ouvert (A=0)

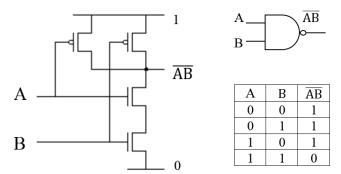

# I.2. La porte NAND

La porte de négation de AND (NAND) présente en entrée deux valeurs 0 ou 1. Si les deux entrées sont à état haut, la sortie est à niveau bas. Et si au moins une des deux entrées est à un niveau bas, cette sortie vaut 1.

Le circuit de la porte *NAND* en logique CMOS peut être formé de quatre transistors dont deux n-MOS et deux p-MOS.

Figure. II. 5 : Schéma et symbole de la porte NAND

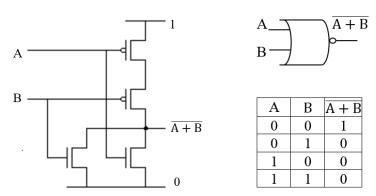

# I.3. La porte NOR

La porte NOR (Non de OR) (Fig. II.6) prend en entrée deux valeurs 0 ou 1. La sortie est basse si au moins une des entrées est à 1 et elle est haute si les deux entrées sont à 0.

En logique CMOS, le circuit de la porte NOR peut être former de quatre transistors dont deux n-MOS et deux p-MOS.

Figure. II. 6 : Schéma et symbole de la porte NOR

Les deux transistors P en parallèle dans le circuit du *NAND* sont en série dans le circuit de la porte *NOR*, Et contrairement, les deux transistors N en série dans le circuit de la porte *NAND* sont en parallèle dans le circuit de la porte *NOR*. Donc le circuit de la porte NOR (Fig. II.6) est le circuit dual du celui de la porte *NAND*

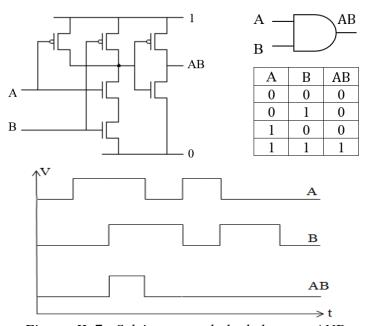

## I.4. Les portes AND et OR :

En remplaçant chaque transistor n-MOS du schéma de la porte *NOR* par un transistor p-MOS et inversement, on obtient le schéma de la porte *AND*.

Les circuits des portes *AND* et *OR* sont respectivement obtenus en combinant un circuit de la porte *NAND* et *NOR* avec un inverseur.

Figure. II. 7 : Schéma et symbole de la porte AND

#### Fonctionnement d'une porte AND

A.B = 1 si et seulement si A = 1 et B = 1

#### **Exemple**

La porte *AND* (Fig. II.7) prend en entrée deux valeurs 0 ou 1. La sortie est au niveau haut si les deux entrées valent 1 et elle est au niveau bas sinon. La table de vérité est donnée cidessous.

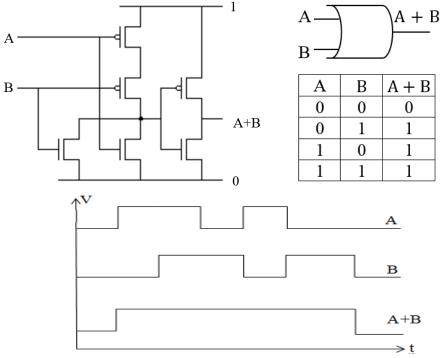

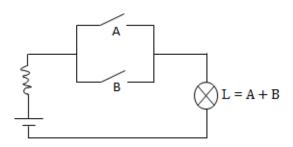

La porte *OR* (*Fig. II.8*) prend en entrée deux valeurs 0 ou 1. La sortie est au niveau bas si les deux entrées valent 0 et elle est au niveau haut sinon.

Figure. II. 8 : Schéma et symbole de la porte OR

# Fonctionnement de la porte OU (OR)

A+B =1 si et seulement si l'une au moins des deux variables vaut 1.

## Exemple:

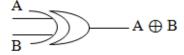

# I.5. La Porte OU exclusif (XOR):

Soient A et B les entrées d'une porte XOR ; la sortie s'écrit dans ce cas : A  $\oplus$  B Symbole :

## Table de vérité:

| A | В | A⊕B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

La sortie A

B vaut 1 si les deux entrées sont différentes

# I.6. La Porte NON OU exclusif (NXOR):

| A | В | $\overline{A \oplus B}$ |

|---|---|-------------------------|

| 0 | 0 | 1                       |

| 0 | 1 | 0                       |

| 1 | 0 | 0                       |

| 1 | 1 | 1                       |

$$\frac{A}{B}$$

$\overline{A \oplus B}$

La sortie A

B vaut 1 si les deux entrées sont égales.

# II. Les différentes relations logiques :

| Α | В | AB |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 0  |

| 1 | 0 | 0  |

| 1 | 1 | 1  |

| A | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

Loi de commutativité :  $\begin{cases} A+B=B+A \\ A.B=B.A \end{cases}$

Loi de distributivité :  $\begin{cases} A(B+C) = AB + AC \\ A + (BC) = (A+B).(A+C) \end{cases}$

Loi d'association :  $\begin{cases} A + (B + C) = (A + B) + C = A + B + C \\ A (B C) = (A B) C = A B C \end{cases}$

Elements Neutres :  $\begin{cases} A + 0 = A \\ A \cdot 1 = A \end{cases}$

Elements Absorbants :  $\begin{cases} A+1=1 \\ A.0=0 \end{cases}$

Loi d'Indépendance :  $\begin{cases} A + A = A \\ A. A = A \end{cases}$

Loi de Complémentarité :  $\begin{cases} A + \bar{A} = 1 \\ A. \bar{A} = 0 \end{cases}$

# Lois d'absorption:

$$A + AB = A$$

$$A(A + B) = A$$

$$A + \bar{A}B = A + B$$

$$A(\bar{A} + B) = AB$$

#### II.1. Théorème de MORGAN

$\underline{1}^{\text{er}}$  théorème : Le complément d'un produit des variables est égal à la somme des compléments des variables.

$$\overline{A.B.C} = \overline{A} + \overline{B} + \overline{C}$$

<u>2em théorème</u>: Le complément d'une somme des variables est égal au produit des compléments des variables.

$$\overline{A + B + C} = \overline{A} \cdot \overline{B} \cdot \overline{C}$$

# II.2. Les fonctions logiques

Toute fonction logique peut être réalisée de la manière suivante :

Soit avec des opérateurs ET, OU, NON (AND, OR, NOT)

Soit avec des opérateurs NON ET (NAND)

Soit avec des opérateurs NON OU (NOR)

On appel fonction logique une combinaison de plusieurs variables booléenne (0 ou 1) reliées par des opérateurs logiques.

Ex.

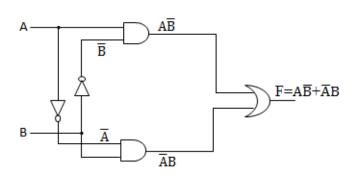

Soit  $F=A\overline{B} + \overline{A}B$

#### Logigramme:

## Mise sous forme algébrique :

Tout circuit logique; quelque soit sa complexité peut être décrit au moyen des opérations booléenne

Ex.

Sans les parenthèses, notre interprétation sera erronée

Car x=A+B.C signifie que A est réuni dans une porte OU avec le produit B.C.

Pour lever cette indétermination, c'est les opérateurs ET qui sont appliqués en premier, sauf s'il y'a des parenthèses.

#### II.3. Table de vérité

On peut représenter une fonction logique de n variables  $f(x_1, x_2, ..... x_n)$  par un tableau de  $2^n$  lignes et n+1 colonnes (n colonnes pour n variables et une colonne pour la fonction).

L'ordre des combinaisons sera croissant du haut vers le bas, et elles seront écrites dans le code binaire naturel (CBN).

| Xn | <br>X2 | $\mathbf{x}_1$ | F |

|----|--------|----------------|---|

| 0  | <br>0  | 0              |   |

|    | :      | :              | • |

|    | :      | :              | • |

|    | :      | :              | • |

| 1  | <br>1  | 1              |   |

Table II.1 : Table de vérité pour une fonction à n Variables

## Exemple:

$F = \overline{A} B + B\overline{C} + ABC = F(A, B, C)$

3 variables  $\rightarrow 2^3$  combinaisons 8 lignes.

| Equivalent<br>Décimal | A | В | С | Ā | C | ĀB | В <del>С</del> | ABC | F |

|-----------------------|---|---|---|---|---|----|----------------|-----|---|

| 0                     | 0 | 0 | 0 | 1 | 1 | 0  | 0              | 0   | 0 |

| 1                     | 0 | 0 | 1 | 1 | 0 | 0  | 0              | 0   | 0 |

| 2                     | 0 | 1 | 0 | 1 | 1 | 1  | 1              | 0   | 1 |

| 3                     | 0 | 1 | 1 | 1 | 0 | 1  | 0              | 0   | 1 |

| 4                     | 1 | 0 | 0 | 0 | 1 | 0  | 0              | 0   | 0 |

| 5                     | 1 | 0 | 1 | 0 | 0 | 0  | 0              | 0   | 0 |

| 6                     | 1 | 1 | 0 | 0 | 1 | 0  | 1              | 0   | 1 |

| 7                     | 1 | 1 | 1 | 0 | 0 | 0  | 0              | 1   | 1 |

# II.4. Formes canoniques:

Toutes les fonctions logiques peuvent se mettre sous 2 formes standards appelées formes canoniques :

<u> $1^{ere}$  forme canonique</u>: somme canonique  $\sum \prod$

Une fonction logique de n variables binaires est écrite sous la forme d'une somme canonique si chacun de ces termes (monômes) est un produit de n éléments pris parmi les n variables ou leurs compléments.

<u>Ex.</u>

F = AB + AB + B

$2^{eme}$  forme canonique: produit canonique  $\prod \sum$

Une fonction logique de n variables binaires est écrite sous la forme d'un produit de somme si chacun de ses termes est une somme de n éléments pris parmi les n variables ou leurs compléments.

<u>Ex.</u>

$F = (\overline{A} + B).(A + \overline{B}).(A + \overline{B})$

*Exemple*: Soit la fonction F définie par la table de vérité suivante:

| Code Décimal | Α | В | С | F |

|--------------|---|---|---|---|

| 0            | 0 | 0 | 0 | 0 |

| 1            | 0 | 0 | 1 | 0 |

| 2            | 0 | 1 | 0 | 0 |

| 3            | 0 | 1 | 1 | 1 |

| 4            | 1 | 0 | 0 | 0 |

| 5            | 1 | 0 | 1 | 1 |

| 6            | 1 | 1 | 0 | 1 |

| 7            | 1 | 1 | 1 | 1 |

Exprimer la fonction F sous forme deux formes canoniques :

## $1^{er}$ Forme:

La fonction F vaux 1 pour :

| Combinaisons | Monômes correspondants |

|--------------|------------------------|

| 011          | ĀBC                    |

| 101          | ABC                    |

| 110          | AB <del>C</del>        |

| 111          | ABC                    |

Et par suite :  $F = \overline{A}BC + A\overline{B}C + AB\overline{C} + ABC$

Ainsi la fonction F est écrite sous la forme de somme de termes de trois variables.

## $2^{eme}$ Forme:

La fonction F vaux 0 pour :

| Combinaisons | Monômes correspondants                   |

|--------------|------------------------------------------|

| 000          | $\overline{A} \overline{B} \overline{C}$ |

| 001          | $\overline{A}$ $\overline{B}$ C          |

| 010          | $\overline{A} \overline{BC}$             |

| 100          | A B C                                    |

## Et par suite:

$$\overline{F} = \overline{A} \overline{B} \overline{C} + \overline{A} \overline{B} C + \overline{A} \overline{B} \overline{C} + \overline{A} \overline{B} \overline{C}$$

$$F = (A + B + C).(A + B + \overline{C}).(A + \overline{B} + C).(\overline{A} + B + C)$$

Ainsi est écrite sous forme de produit de somme de variables.

# II.5. Expression numérique:

On peut représenter une fonction logique par la valeur décimale (numéro de la ligne de la table de vérité) de chaque combinaison des variables pour la quelle la fonction logique vaut 1.

#### Exemple:

$\overline{F} = \overline{A} \overline{B} \overline{C} + \overline{A} \overline{B}C + \overline{A} BC + AB \overline{C} + ABC$

| Code Décimal | Α | В | С | F |

|--------------|---|---|---|---|

| 0            | 0 | 0 | 0 | 1 |

| 1            | 0 | 0 | 1 | 1 |

| 2            | 0 | 1 | 0 | 0 |

| 3            | 0 | 1 | 1 | 1 |

| 4            | 1 | 0 | 0 | 0 |

| 5            | 1 | 0 | 1 | 0 |

| 6            | 1 | 1 | 0 | 1 |

| 7            | 1 | 1 | 1 | 1 |

On peut écrire :  $F = \sum (0,1,3,6,7)$  ou  $\overline{F} = \sum (2,4,5)$

# III. Matrice de combinaisons (Tableau de KARNAUGH)

Ce tableau est comparable à la table de vérité.

Pour une fonction F de n variables, le TK sera composé de 2n cases contenant les états de la fonction F (0 ou 1) correspondant aux 2<sup>n</sup> combinaisons possibles de n variables. Ces variables sont représentés sur deux axes, de plus elles sont disposées de telle façon qu'un seul bit d'entrée change d'état au passage d'une case à une case voisine (adjacente). Les combinaisons seront donc représentées dans le code binaire réfléchi.

## Exemple:

TK pour une fonction à 3 variables

Soit une fonction F à 3 variables A, B et C définie par la TV suivante:

| Code Décimal | A | В | C | F |

|--------------|---|---|---|---|

| 0            | 0 | 0 | 0 | 0 |

| 1            | 0 | 0 | 1 | 0 |

| 2            | 0 | 1 | 0 | 0 |

| 3            | 0 | 1 | 1 | 1 |

| 4            | 1 | 0 | 0 | 0 |

| 5            | 1 | 0 | 1 | 1 |

| 6            | 1 | 1 | 0 | 1 |

| 7            | 1 | 1 | 1 | 1 |

Construire le tableau de Karnaugh correspondant à cette fonction.

3 variables réparties en deux groupes :

Le tableau de KARNAUGH contient  $2^3$  cases :  $\begin{cases} 1 \text{ variable sur la verticale} \\ 2 \text{ variables sur l'horizontale} \end{cases}$

| A | BC | 00 | 01 | 11 | 10 |

|---|----|----|----|----|----|

| 0 |    |    |    |    |    |

| 1 |    |    |    |    |    |

4 variables 2<sup>4</sup> cases : { 2 variables sur la verticale 2 variables sur l'horizontale

| AB | ВС | 00 | 01 | 11 | 10 |

|----|----|----|----|----|----|

| 00 |    |    |    |    |    |

| 01 |    |    |    |    |    |

| 11 |    |    |    |    |    |

| 10 |    |    |    |    |    |

# **Chapitre III: Simplification des Fonctions Logiques**

.....

#### **Introduction:**

Puisque la réalisation d'une fonction logique n'est pas unique, il est souvent souhaitable pour des raisons d'optimisation de disposer de sa forme minimale.

La simplification à cette forme minimal peut être faite de deux façons différentes : une première qui est fondée sur l'application des lois et des théorèmes de l'algèbres booléenne et une deuxième qui est une méthode graphique qui suit une démarche systématique.

# I. Simplification Algébrique

La simplification algébrique est un processus d'approximation successive basée sur deux étapes essentielles :

- 1- La transformation par applications successives des théorèmes de MORGAN et par multiplication des termes de l'expression pour obtenir une somme de produits.

- 2- La vérification de chaque produit pour trouver les variables communes afin d'éliminer un ou plusieurs termes.

## **Exemple**

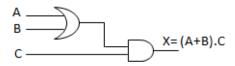

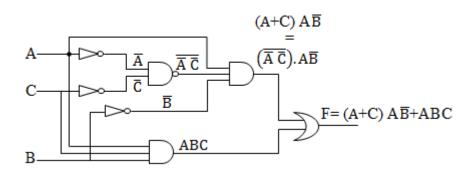

Simplifier par la méthode algébrique le circuit logique suivant :

La première étape consiste à établir l'expression de la sortie  $F = (A+C) A \overline{B} + ABC$

# *1*<sup>ère</sup> étape de simplification:

Obtenir la somme de produits :  $F = A\overline{B} + A\overline{B}C + ABC$

<u>2<sup>eme</sup> étape de simplification:</u>

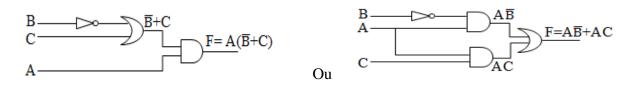

$$F = A\overline{B} + AC (B + \overline{B}) = A\overline{B} + AC$$

Le circuit logique simplifier est donné par:

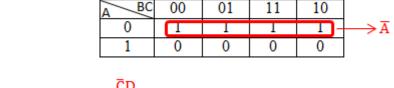

# II. Simplification par la méthode de KARNAUGH (Graphique)

Dés qu'un T K est rempli de "1" et "0", il s'agit pour obtenir l'expression de la forme F sous forme d'une somme de produit d'additionner logiquement les cases qui contiennent un "1".

#### Ex.

Soit la fonction F définie par le TK suivant :

| AB CD | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 0  | 0  | 1  | 1  |

| 01    | 0  | 0  | 0  | 0  |

| 11    | 0  | 0  | 0  | 0  |

| 10    | 1  | 0  | 0  | 1  |

$$F = \overline{A} \, \overline{B}CD + \overline{A}\overline{B}C\overline{D} + A\overline{B}\overline{C}\overline{D} + A\overline{B}C\overline{D}$$

Il est possible de simplifier l'expression de F en combinant selon des règles précises les cases du tableau qui contiennent des 1.

On donne à ce processus de combinaison le nom réunion.

#### a- Réunion des doublets (paires):

Soient les T K représentés ci-dessous :

| A BC | 00 | 01 | 11 | 10 |  |  |

|------|----|----|----|----|--|--|

| 0    | 0  | 1  | 1  | 0  |  |  |

| 1    | 0  | 0  | 0  | 0  |  |  |

| (a)  |    |    |    |    |  |  |

| A BC | 00 | 01 | 11 | 10 |  |  |

|------|----|----|----|----|--|--|

| 0    | 0  | П  | 0  | 0  |  |  |

| 1    | 0  | 1  | 0  | 0  |  |  |

| (b)  |    |    |    |    |  |  |

Dans le TK a, il y'a deux 1 qui sont voisins horizontalement, le premier a les coordonnées  $\overline{ABC}$ , tandis que le second à les cordonnées  $\overline{ABC}$ .

Dans ces deux termes, seule la variable B change d'état, donc ces deux termes peuvent êtres réunis en éliminant la variable B. donc le résultat est  $\overline{AC}$ .

Le même procédé peut être appliqué au tableau (b) ou les deux 1 sont voisins verticalement.

En regroupant ces deux 1 on élimine la variable 1 car c'est la seule qui change d'état.

Donc on aura en résultat BC

#### **Exemple**

| A BC | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  | 0  | 0  |

| 1    | 1  | 0  | 0  | 1  |

Il existe deux 1 situés dans la colonne de droite et dans la colonne de gauche (sur la même ligne). Ces deux "1" sont également adjacentes leurs réunion élimine la variable B.

$X = A\overline{C}$

### Exemple2

Simplifier la fonction F définie par le TK suivant :

| AB CD | 00 | 01 | 11 | 10  |                                             |

|-------|----|----|----|-----|---------------------------------------------|

| 00    | 0  | 0  | 1  |     | $\longrightarrow \overline{A}\overline{B}C$ |

| 01    | 0  | 0  | 0  | 1   |                                             |

| 11    | 0  | 0  | 0  | 0   |                                             |

| 10    | 1  | 0  | 0  | 1 - | →ABD                                        |

Dans ce tableau deux doublet peuvent êtres réunis, celui formé par les "1" adjacents horizontalement et celui formé par les "1" de la colonne de gauche et droite.

Le résultat de ces réunions  $F = \overline{ABC} + A\overline{BD}$

En résumé : la réunion d'un doublet de 1 adjacents dans un TK élimine la variable qui qui est à la fois non complémentée et complémentée.

#### b-Réunion en groupe de quatre:

Il peut arriver qu'un TK contienne quatre "1" qui soient adjacents La figure suivante illustre plusieurs exemples de telles réunions.

|       |    |    | 700 |    |

|-------|----|----|-----|----|

| AB CD | 00 | 01 | /11 | 10 |

| 00    | 0  | П  | 0   | 0  |

| 01    | 0  | 1  | 0   | 0  |

| 11    | 0  | 1  | 0   | 0  |

| 10    | 0  | 1  | 0   | 0  |

| AB CD | 00 | 01 | 11  | 10 |      |

|-------|----|----|-----|----|------|

| 00    | 0  | 0  | 0   | 0  |      |

| 01    | 0  | Π  | 1)- | 0  | A DD |

| 11    | 0  | 1  | 1   | 0  | → BD |

| 10    | 0  | 0  | 0   | 0  |      |

| AB CD | 00 | 01 | 11 | 10 |      |

|-------|----|----|----|----|------|

| 00    | 0  | 0  | 0  | 0  |      |

| 01    | 0  | 0  | 0  | 0  |      |

| 11    | 1  | 0  | 0  | Τ_ | →AD̄ |

| 10    | 1  | 0  | 0  | 1  | - AD |

| AB CD | 00 | 01 | 11 | 10 |      |

|-------|----|----|----|----|------|

| 00    | Τ  | 0  | 0  |    | 4    |

| 01    | 0  | 0  | 0  | 0  | B̄D̄ |

| 11    | 0  | 0  | 0  | 0  |      |

| 10    | 1  | 0  | 0  | 1  |      |

Quand en réunis des groupes de quatre on ne retrouve que dans le terme résultant que les variables qui restent sous la même forme dans toutes les cases

| AB CD | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 0  | 0  | П  | 0  |

| 01    | П  |    | 1  | 0  |

| 11    | 0  | П  |    | 1  |

| 10    | 0  | 1  | 0  | 0  |

$$F = \overline{A}B\overline{C} + \overline{A}CD + ABC + A\overline{C}D$$

En Résumé: la réunion des groups de quatre 1 adjacents élimine les deux variables qui sont à la fois non complémentées et complémentées.

## c-Réunion en groupe de huit (octets):

La réunion d'un octet dans un TK donne lieu à l'élimination de 3 variables.

Ex.

# II.1. Le processus de simplification au complet

Il est claire que plus on à des 1 dans le regroupement, plus le nombre de variables éliminées est grand,

Donc pour simplifier l'expression logique d'un T.K il suffit de trouver le minimum de groupements associant le maximum de "1" adjacents.

Ex: Soit la fonction F définie par le TK suivant:

| AB CD | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 0  | 0  | П  | 0  |

| 01    | 1  | 1  | 1  |    |

| 11    | 1  | 1  | 0  | 0  |

| 10    | 0  | 0  | 0  | 0  |

Il existe deux groupements de 4 et un groupement de 2  $\,$

$$F = B\overline{C} + \overline{A}B + \overline{A}CD$$

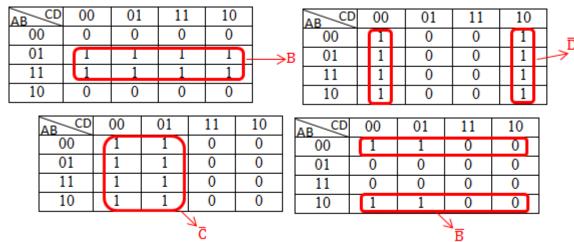

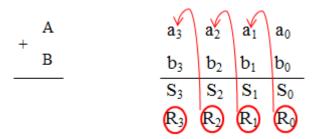

## II.2. Les conditions indifférentes

Certains circuits logiques peuvent être conçus pour que certaines conditions d'entrée ne correspondent à aucun niveau de sortie particulier (ni haute ni basse).

Ceci est illustré par l'exemple suivant.

| A BC | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  | 1  | Ø  |

| 1    | 0  | Ø  | 1  | 1  |

La table de vérité est :

Dans ces deux tables, aucune valeur de F ne figure pour les conditions :

$$A,B,C = 0,1,0$$

et  $A,B,C = 1,0,1$

Un concepteur de circuit est libre de mettre des "0" et des "1" vis-à-vis des conditions indifférentes, en vue de produire l'expression de sortie la plus simple

## Exemple 1

Dans le TK précèdent nous devons décider quel Ø de sortie est remplacé par un 1 et quel Ø est remplacer par un 0 pour donner l'expression la plus simple.

| A BC | 00 | 01 | 11 | 10 |       |

|------|----|----|----|----|-------|

| 0    | 0  | 0  |    | Ø  | F = B |

| 1    | 0  | Ø  | 1  | 1  | т — Б |

## Exemple2

Simplifier la fonction F définie par la TV suivante :

| Α                                                                  | В                                                        | С                                                                  | D                                                        | S                                                                       |

|--------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|

| 0                                                                  | 0                                                        | 0                                                                  | 0                                                        |                                                                         |

| 0                                                                  | 0                                                        | 0                                                                  | 1                                                        | 1                                                                       |

| 0                                                                  | 0                                                        | 1                                                                  | 0                                                        | Ø                                                                       |

| 0                                                                  | 0                                                        | 1                                                                  | 1                                                        | 1                                                                       |

| 0                                                                  | 1                                                        | 0                                                                  | 0                                                        | 1                                                                       |

| 0                                                                  | 1                                                        | 0                                                                  | 1                                                        | 1                                                                       |

| 0                                                                  | 1                                                        | 1                                                                  | 0                                                        | 0                                                                       |

| 0                                                                  | 1                                                        | 1                                                                  | 1                                                        | 0                                                                       |

| 1                                                                  | 0                                                        | 0                                                                  | 0                                                        | 1                                                                       |

| 1                                                                  | 0                                                        | 0                                                                  | 1                                                        | Ø                                                                       |

| 1                                                                  | 0                                                        | 1                                                                  | 0                                                        | 0                                                                       |

| 1                                                                  | 0                                                        | 1                                                                  | 1                                                        | 1                                                                       |

| 1                                                                  | 1                                                        | 0                                                                  | 0                                                        | 0                                                                       |

| 1                                                                  | 1                                                        | 0                                                                  | 1                                                        | 0                                                                       |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>1<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0 |

| 1                                                                  | 1                                                        | 1                                                                  | 1                                                        | Ø                                                                       |

| AB CD | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    | L) |    | Ø  |

| 01    | 1  | 1  | 0  | 0  |

| 11    | 0  | 0  | Ø  | Ø  |

| 10    | 1  | Ø  | 1  | 0  |

$$S = \overline{A}\overline{C} + \overline{A}\overline{B} + \overline{B}\overline{C} + \overline{B}D$$

<u>NB.</u> Cette fonction peut être définie de la manière suivante :

$$S = \sum (0,1,3,4,5,8,11) + \emptyset(2,9,14)$$

## II.3. Récapitulation

La méthode de simplification avec TK plusieurs avantages comparativement à la méthode algébrique, mais elle reste peut efficace pour les fonctions à grand nombre de variables.

| AB CDE | 000 | 001 | 011 | 010 | 110 | 111 | 101 | 100 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| 00     |     |     |     |     |     |     |     |     |

| 01     |     |     |     |     |     |     |     |     |

| 11     |     |     |     |     |     |     |     |     |

| 10     | ·   |     | ·   |     |     |     |     |     |

# III. Les Circuits arithmétiques

# III.1. Additionneur binaires

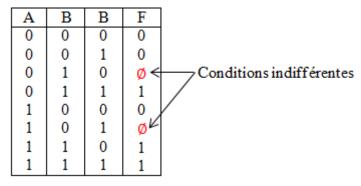

#### III.1.1. Demi-additionneur

Soit deux chiffres binaires a et b à additionner.

Quatre cas se présentent alors :

| a | b | S | R |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

## **Equation logique:**

$$S = \bar{a}b + a\bar{b} = a \oplus b$$

$$R = ab$$

Figure III.1: Demi-Additionneur

Le circuit qui réalise S et R s'appel demi additionneur. C'est un circuit qui ne permet pas de tenir compte de la retenue précédente.

Pour Y parvenir on utilise un additionneur complet.

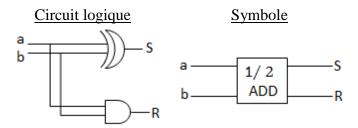

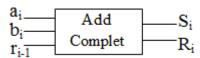

# III.1.2. Additionneur complet

Soient a et b deux nombre a quatre bits chacun.

La somme S de A et B est obtenue de la manière suivante :

Figure III.2: Processus d'addition sur 4bits

Nous remarquons qu'a chaque étape de l'addition, nous additionnons 3 bits :  $a_i$ ,  $b_i$  et le bit de retenue provenons du rang précédent  $r_{i-1}d$ . Le résultat de l'addition de ces 3 bits est un nombre à deux bits : le bit de la somme S et le bit de retenue R. ce dernier doit être ajouté au rang a gauche, d'où la TV suivante:

| $a_{i}$ | b <sub>i</sub> | $r_{i-1}$ | $S_{i}$ | Ri |

|---------|----------------|-----------|---------|----|

| 0       | 0              | 0         | 0       | 0  |

| 0       | 0              | 1         | 1       | 0  |

| 0       | 1              | 0         | 1       | 0  |

| 0       | 1              | 1         | 0       | 1  |

| 1       | 0              | 0         | 1       | 0  |

| 1       | 0              | 1         | 0       | 1  |

| 1       | 1              | 0         | 0       | 1  |

| 1       | 1              | 1         | 1       | 1  |

## Symbole

Figure III.3: Additionneur Complet

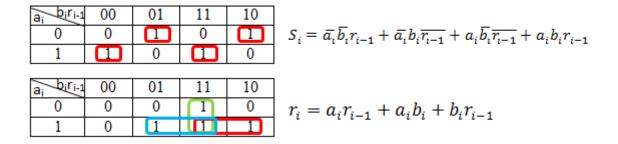

## Simplification par le T.K:

L'expression pour S<sub>i</sub> devient :

$$S_{i} = \overline{a}_{i}(\overline{b}_{i}r_{i-1} + b_{i}\overline{r_{i-1}}) + a_{i}(\overline{b}_{i}\overline{r_{i-1}} + b_{i}r_{i-1})$$

$$= \overline{a}_{i}(b_{i}\oplus r_{i-1}) + a_{i}(\overline{b_{i}\oplus r_{i-1}})$$

$$S_{i} = a_{i}\oplus (b_{i}\oplus r_{i-1})$$

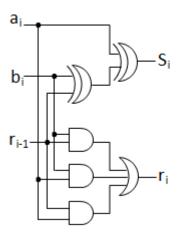

Les expressions de Si et Ri peuvent être matérialisées par le circuit logique suivant :

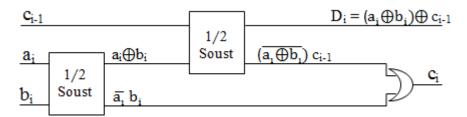

Figure III.4: Circuit d'un Additionneur Complet

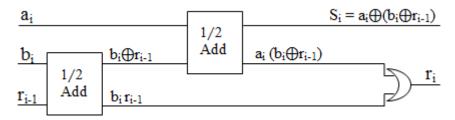

# III.1.3. Additionneur complet à l'aide de deux demi-additionneurs

Reprenons les deux expressions logiques de S<sub>i</sub> et r<sub>i</sub> :

$$S_i = a_i \oplus (b_i \oplus r_{i-1})$$

$$r_i = a_i r_{i-1} + a_i b_i + b_i r_{i-1}$$

Ou

| a <sub>i</sub> b <sub>i</sub> r <sub>i-1</sub> | 00 | 01 | 11 | 10 | $r_i = b_i r_{i-1} + a_i b_i r_{i-1} + a_i b_i \overline{r_{i-1}}$ |

|------------------------------------------------|----|----|----|----|--------------------------------------------------------------------|

| 0                                              | 0  | 0  | П  | 0  | 1 (1.0)                                                            |

| 1                                              | 0  |    | 1  |    | $r_i = b_i r_{i-1} + a_i (b_i \oplus r_{i-1})$                     |

Les équations logiques d'un demi-additionneur sont les suivantes :

$$a \longrightarrow 1/2 \longrightarrow S$$

$S = a \oplus b$

$b \longrightarrow Add \longrightarrow r$   $R = ab$

Pour concevoir un additionneur complet a l'aide d'un demi-additionneur :

Figure III.5 : Additionneur complet à l'aide des Demi-Additionneurs

# III.1.4. Conception d'un additionneur binaire parallèle

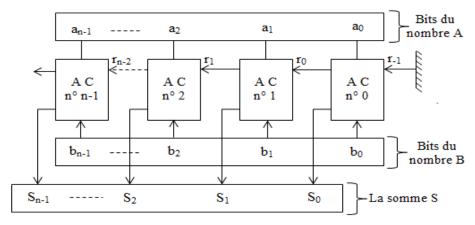

On va concevoir un circuit logique qui effectue la somme de deux nombres binaires A et B à n bits chacun. L'opération consiste à accoler des additionneurs complets identiques pour chaque rang binaire.

Figure III.6 : Additionneur Binaire Parallèle

Les bits correspondant des nombres  $a_i$  et  $b_i$  et le bit de retenue généré par l'addition précédente sont appliqués a des additionneurs complets.

Par exemple, les bits  $a_1$  et  $b_1$  sont transmis a l'AC1 en meme temps que  $r_0$  qui est le bit de retenue produit par l'addition de  $a_0$  et  $b_0$ .

Ce montage est appelé un additionneur parallele car tout les bits sont appliqués et et additionnés simultanément.

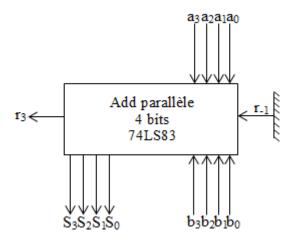

# III.1.5. Additionneur parallèle intégré

L'un des plus courants boitiers (CI) d'additionneurs parallèles de 4 bits sont 7483A, 74LS83A, 74283 et 74LS283...

Le symbole logique du 74LS83 est le suivant :

Figure III.7 : Additionneur parallèle intégré

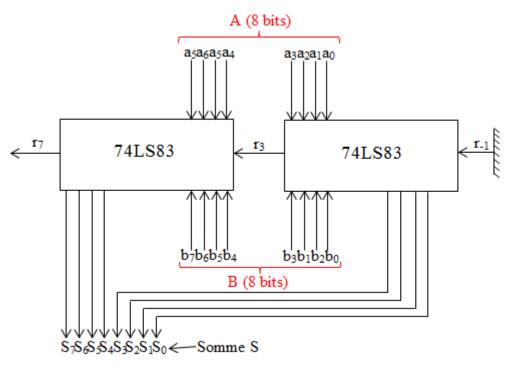

## III.1.6. Montage en cascade d'additionneurs paralleles

Il est possible de raccorder deux ou plusieurs add paralleles en cascade afin d'additionner des nombres ayant un plus grand nombre de bits

Figure III.8 : Deux additionneurs paralleles montés en cascade

#### Exemple

Soient les deux nombres A et B donnés par : A = 10001001 Il n'y a donc pas de déppasement sur le bit 7  $(r_7=0)$  B = 01001000

S = 11010001

#### III.2. Soustractions binaires

## III.2.1. Demi-Soustracteur

La différence D et la retenue C de deux nombres A et B sont présentées par la TV suivante :

| A | В | D | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

#### Equations logiques:

$$D = \overline{A}B + \overline{B}A$$

$$= A \oplus B$$

$$C = \overline{A}B$$

### <u>Circuit logique:</u>

Figure III.9: Demi-soustracteur

#### III.2.2. Soustracteur complet:

A l'aide de deux demi soustracteurs on peut réalisé un soustracteur complet présenté par la TV suivante :

| a <sub>i</sub> | b <sub>i</sub> | $C_{i-1}$ | Di | Ci |

|----------------|----------------|-----------|----|----|

| 0              | 0              | 0         | 0  | 0  |

| 0              | 0              | 1         | 1  | 1  |

| 0              | 1              | 0         | 1  | 1  |

| 0              | 1              | 1         | 0  | 1  |

| 1              | 0              | 0         | 1  | 0  |

| 1              | 0              | 1         | 0  | 0  |

| 1              | 1              | 0         | 0  | 0  |

| 1              | 1              | 1         | 1  | 1  |

| a <sub>i</sub> b <sub>i</sub> c <sub>i-1</sub> | 00                                            | 01 | 11 | 10 |  |  |  |  |  |

|------------------------------------------------|-----------------------------------------------|----|----|----|--|--|--|--|--|

| 0                                              |                                               | 0  | Θ  | 0  |  |  |  |  |  |

| 1                                              | 0                                             | Θ  | 0  |    |  |  |  |  |  |

| $D_{i} = (a_{i}$                               | $D_{i} = (a_{i} \oplus b_{i}) \oplus c_{i-1}$ |    |    |    |  |  |  |  |  |

| h:C: 4                                         | 00                                            | 01 | 11 | 10 |  |  |  |  |  |

| ai Aloi-1                                      | 00                                            | 01 | 11 | 10 |  |  |  |  |  |

| 0                                              | 0                                             | Ü  | 1  | 1  |  |  |  |  |  |

| 0                                              | 0                                             | 1  |    | 0  |  |  |  |  |  |

Figure III.10 : Soustracteur Complet à l'aide des Demi-Soustracteurs

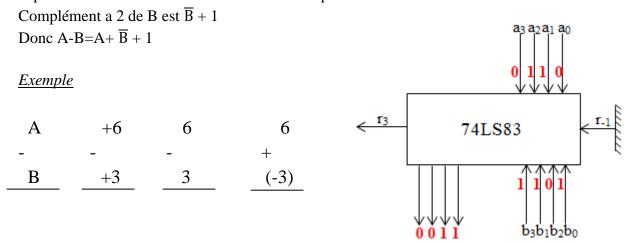

# III.2.3. Notation complément à deux

L'addition et la soustraction des nombres signés se résument à une simple addition si on exprime ces nombres selons la notation en complément à 2.

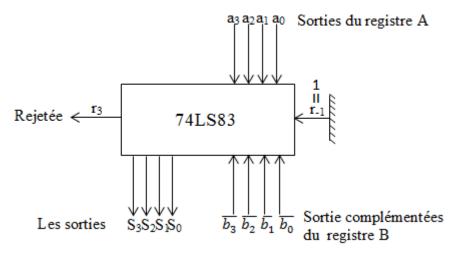

L'additionneur parallele produit alors la somme 0011 en sortie, et qui correspond a +3. La retenue  $r_3$  est à 1, mais cette retenue est rejetée dans la méthode complément à deux. La figure suivante illustre un additionneur peut servir à la soustraction :

Figure III.11 : Additionneur parallele seravnt à soustraire

On utilise les sorties complémentées du registre B pour complémenté B à 1, et en plus en transforme r<sub>-1</sub> à un 1 qui va etre ajouté au poid le plus faible de l'additionneur a fin d'obtenir le complément à 2 de B.

Donc S est le résultat de la soustraction et r<sub>3</sub> est le signe de ce résultat.

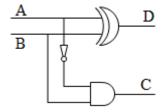

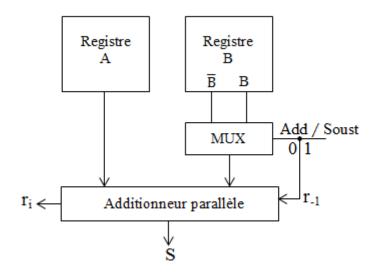

## III.3. Additionneur / Soustracteeur

Le circuit suivant est à la fois add et soust complet dans la notation complément à 2.

Figure III.12: Additionneur / Soustracteur

Cet Additinneur / Soustracteur est commandé par le signal de commande Add / Soust. Quand ce signal est au niveau BAS, le circuit fonctionne comme un additionneur Quand ce signal est au niveau HAUT, le circuit fonctionne comme un soustracteur.

#### **III.4. Additionneur BCD:**

Rappelons que ce code fait correspondre a chaque nombre décimal un code binaire de quatre bites compris entre 0000 et 1001

L'addition avec le code BCD présente deux cas :

#### a- Somme infèrieure ou égale à 9 :

#### Exemple 1

Additionnons 5 et 4 en utilisant leurs représentation BCD :

L'addition est éffectuée comme une addition binaire normale

#### Exemple2

Dans ce cas l'addition est un processus direct équivalent à l'addition binaire.

#### b- Somme superieure à 9 :

#### Exemple

Additionnons 6 et 7 en BCD:

1101 n'existe pas en code BCD, dans un tel cas il faut corriger la somme en ajoutant 6(0110) afin de sauter 6 valeurs qui présentent un code non valide.

# Chapitre IV: Analyse et synthèse des circuits logiques combinatoires

\_\_\_\_\_

#### I. les circuits combinatoires

Les circuits combinatoires sont des circuits avec lesquels on peut établir plusieurs opérations comme:

- <u>a- Codage et décodage:</u> C'est la transposition des données d'un code à un autre.

- b- Le multiplexage: Choix d'un groupe de données parmi plusieurs.

- c- Le démultiplexage: Aiguillage des données vus une destination parmi plusieurs.

- <u>d-Acheminement par Bus:</u> Transmission de données entre plusieurs dispositifs par d'intermédiaire d'un bus commun.

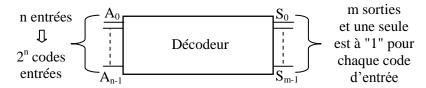

#### II. Le décodeur

Le décodeur est un circuit logique qui établit la correspondance entre un code d'entrée binaire de n bits et m lignes de sortie, pour chacune des combinaisons possibles des entrées, une seule ligne de sortie est validée.

Donc pour chacune des 2<sup>n</sup> combinaisons possibles, une seule est à l'état haut, et toutes les autres deumeurent au niveau bas.

<u>Rq:</u> De nombreux décodeurs sont conçus pour avoir des sorties vraies au niveau bas (sortie active est au niveau bas tandis que toutes les autres sont au niveau haut). Donc le docodeur va présentés des inversions en sortie.

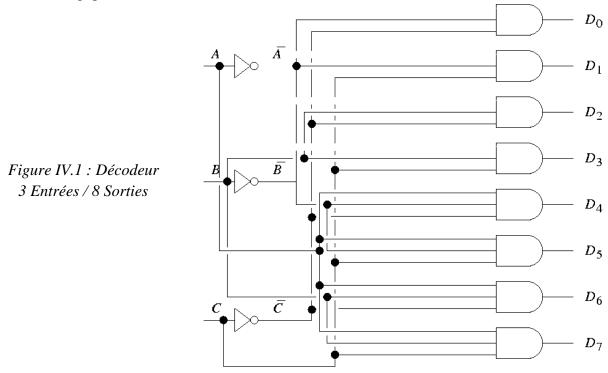

## II.1. Décodeur 3 entrées 8 sorties (1 parmi 8)

C'est un circuit a trois vois d'entrée et 8 vois de sortie. Sa TV est la suivante :

| A | В | С | $D_0$ | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ | $D_0 = \bar{A}\bar{B}\bar{C}$ |

|---|---|---|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|

| 0 | 0 | 0 | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | $D_1 = \bar{A}\bar{B}C$       |

| 0 | 0 | 1 | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | $D_2 = \bar{A}B\bar{C}$       |

| 0 | 1 | 0 | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | $D_3 = \bar{A}BC$             |

| 0 | 1 | 1 | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | _                             |

| 1 | 0 | 0 | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | $D_4 = A\bar{B}\bar{C}$       |

| 1 | 0 | 1 | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | $D_5 = A\bar{B}C$             |

| 1 | 1 | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | $D_6 = AB\bar{C}$             |

| 1 | 1 | 1 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | $D_7 = ABC$                   |

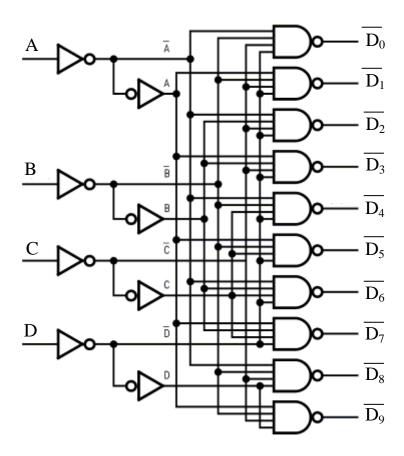

Le circuit logique de ce décoeur est le suivant :

On peut ajouter au décodeur si-dessus une ligne commune qu'on appelle validaion racordé à la quatrième entrée de chaque porte AND. Quand cette ligne est au niveau hau; le décodeur fonctionne normalement, et si elle est gardée au niveau bas, toute les sortie sont forcé au niveau bas quelque soit les niveau appliqués au entrées A,B,C donc ce décodeur est validé seulement si le signal validation est au niveau haut.

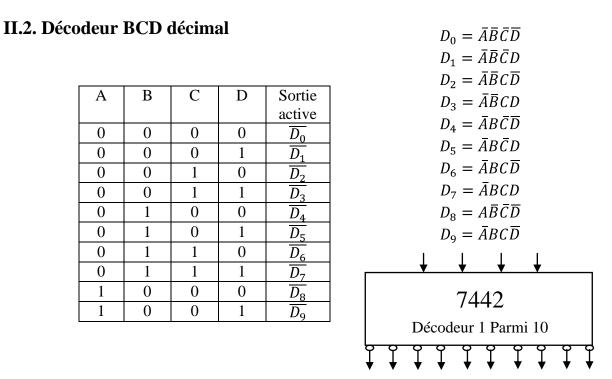

Figure IV.2. Décodeur BCD décimal valide à état bas

Le Décodeur BCD décimal présente en entrée un code binaire a qautre bits et dix lignes de sortie (de 0000 à 1001). Les codes à qautre bits inutilisés (1010 à 1111) n'active aucune des sorties lorqu'ils sont appliqués.

La figure suivante présente le shéma logique d'un décodeur BCD décimal 74XX42

Figure IV.3 : Logigramme d'un décodeur BCD décimal 74XX42

Une sortie ne passe à zéro qu'au moment ou son entrée BCD est appliquée <u>Exemple</u>: DCBA =  $0101 \rightarrow \text{La Sortie } \overline{S5}$  est au niveau 0

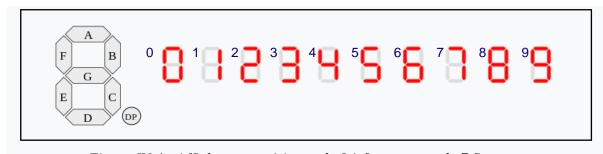

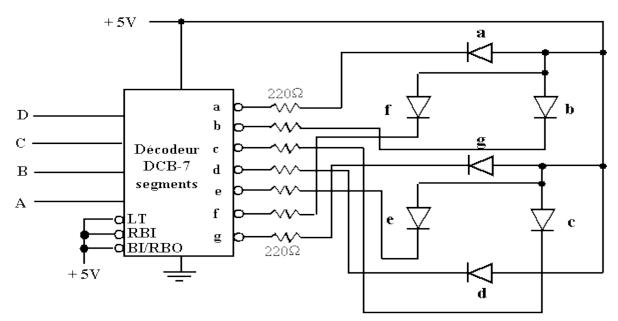

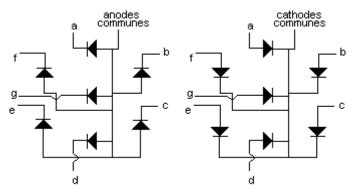

## II.3. Décodeur BCD – 7 Segments

Dans de nombreux affichages numériques les dix chiffres 0 à 9 et parfois les caractères héxadécimaux de A à F sont configurés au moyen de 7 Segments

Figure IV.4 : Affichage numériques de 0 à 9 au moyen de 7 Segments

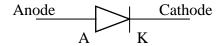

Chaque segment est constitué d'un matériau qui émet de la lumière quand il est traversé par un courant. Les matériaux les plus utilisés sont les diodes électroluminescentes (LED)

Figure IV.5 : LED : diode électroluminescente

| Décimal | A | В | С | D | ā | $\overline{b}$ | $\overline{c}$ | $\bar{d}$ | $\bar{e}$ | $\bar{f}$ | $ar{g}$ |

|---------|---|---|---|---|---|----------------|----------------|-----------|-----------|-----------|---------|

| 0       | 0 | 0 | 0 | 0 | 0 | 0              | 0              | 0         | 0         | 0         | 1       |

| 1       | 0 | 0 | 0 | 1 | 1 | 0              | 0              | 1         | 1         | 1         | 1       |

| 2       | 0 | 0 | 1 | 0 | 0 | 0              | 1              | 0         | 0         | 1         | 0       |

| 3       | 0 | 0 | 1 | 1 | 0 | 0              | 0              | 0         | 1         | 1         | 0       |

| 4       | 0 | 1 | 0 | 0 | 1 | 0              | 0              | 1         | 1         | 0         | 0       |

| 5       | 0 | 1 | 0 | 1 | 0 | 1              | 0              | 0         | 1         | 0         | 0       |

| 6       | 0 | 1 | 1 | 0 | 0 | 1              | 0              | 0         | 0         | 0         | 0       |

| 7       | 0 | 1 | 1 | 1 | 0 | 0              | 0              | 1         | 1         | 1         | 1       |

| 8       | 1 | 0 | 0 | 0 | 0 | 0              | 0              | 0         | 0         | 0         | 0       |

| 9       | 1 | 0 | 0 | 1 | 0 | 0              | 0              | 0         | 1         | 0         | 0       |

Figure IV.6: Afficheur 7 segments à anode commune 7447

Par exemple pour afficher 1 il faut que les segments a et b sont allumés et les autres sont éteins.

Un décodeur 7 segements accepte en entrée les les 7 codes BCD et rend avtive les sorties qui vont permettre de faire passer un courant dans les segments qui forment le chiffre décimal correspondant

Le 7447 est un décodeur 7 segments dont chaque segment est constitué des diodes LED. Les anodes dans ces diodes sont toutes réunies à Vcc (+5V) et leurs cathodes sont connectées a travers des resistances limitatrices de courant aux sorties appropriées du décodeurs.

Ce dernier présente des sorties actives a niveau bas, sa table de vérité et sont circuit sont présentés en *Fig.V.6*.

Exemple : Soit l'entrée DCBA = 0101, qui correspond à 5V, En réponse a cette entrée les sorties

$\overline{a} \ \overline{f} \ \overline{g} \ \overline{c} \ \overline{d}$  sont amenées au niveau bas (racordés à la masse)

Il existe un autre type d'afficheur à 7 segments dit a cathode commune dans lequel toute les cathodes sont réunies à la masse.

Dans cet afficheur les sorties sont vraies au niveau haut (Ex 7448)

Figure IV.7 : Comparaison entre l'Afficheur7 segments à anode commune 7447 et à cathode commune 7448

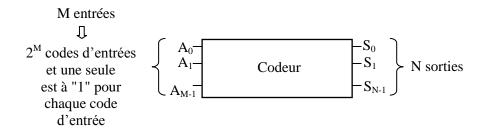

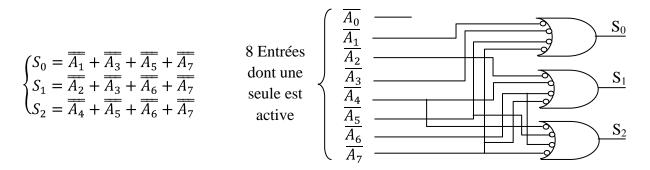

#### **III. Les Codeurs**

Le processus inverse du décodage est le codage présente un circuit logique avec un certain nombre d'entrée (M) dont une seule est active et qui correspond à une représentation de sortie de N bits

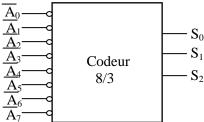

## III.1. Codeur Octal-Binaire (8/3)

Un codeur Octal binaire a 8 vois d'entrée et produit une représentation binaire de 3 bits *Exemple*

Figure IV.8 : Codeur 8entrées/3Sorties active à état bas

| $\overline{A_0}$ | $\overline{A_1}$ | $\overline{A_2}$ | $\overline{A_3}$ | $\overline{A_4}$ | $\overline{A_5}$ | $\overline{A_6}$ | $\overline{A_7}$ | $S_2$ | $S_1$ | $S_0$ |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------|-------|-------|

| Ø                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 0     | 0     | 0     |

| Ø                | 0                | 1                | 1                | 1                | 1                | 1                | 1                | 0     | 0     | 1     |

| Ø                | 1                | 0                | 1                | 1                | 1                | 1                | 1                | 0     | 1     | 0     |

| Ø                | 1                | 1                | 0                | 1                | 1                | 1                | 1                | 0     | 1     | 1     |

| Ø                | 1                | 1                | 1                | 0                | 1                | 1                | 1                | 1     | 0     | 0     |

| Ø                | 1                | 1                | 1                | 1                | 0                | 1                | 1                | 1     | 0     | 1     |

| Ø                | 1                | 1                | 1                | 1                | 1                | 0                | 1                | 1     | 1     | 0     |

| Ø                | 1                | 1                | 1                | 1                | 1                | 1                | 0                | 1     | 1     | 1     |

Par exemple au niveau bas sur  $\overline{A}_3$  toutes les autres entrées sont à 1 et on a la sortie (011) qui représente le code binaire de 3

Figure IV.9: Codeur Octal/Binaire 8/3

NB :  $\overline{A_0}$  n'est pas connéctée à une porte logique puisque les sorties du codeur sont normalement à (000) quand aucune des entrées de  $\overline{A_1}$  a  $\overline{A_7}$  n'est au niveau bas

## III.2. Codeur de priorité

Un codeur de priorité présente une sortie active lorsque deux entrées sont validées, dans un tel codeur quand par exemple les deux entrées  $\overline{A_5}$  et  $\overline{A_3}$  sont activées au même temps ; la répense donnée en sortie est 101 donc la sortie correespond au nombre le plus élevés.

# III.2.1 Codeur de priorité Decimal – BCD

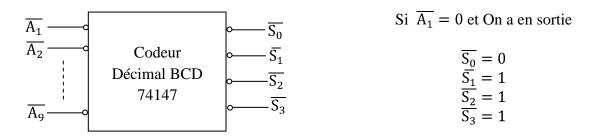

Le symbole logique du codeur de priorité Décimal – BCD (74147) est présenté comme suivant

Figure IV.10 : Codeur de priorité Décimal - BCD

Ce circuit possède 9 entrées vraies au niveau bas représentant les 9 chiffres décimaux (1 à 9) et produit la représentation BCD complémentée correspondante à l'entrée la plus haute mise au niveau vrai

| $\overline{A_1}$ | $\overline{A_2}$ | $\overline{A_3}$ | $\overline{A_4}$ | $\overline{A_5}$ | $\overline{A_6}$ | $\overline{A_7}$ | $\overline{A_8}$ | $\overline{A_9}$ | $\overline{S_3}$ | $\overline{S_2}$ | $\overline{S_1}$ | $\overline{S_0}$ |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| Ø                | Ø                | Ø                | Ø                | Ø                | Ø                | Ø                | Ø                | 0                | 1                | 1                | 1                | 0                |

| Ø                | Ø                | Ø                | Ø                | Ø                | Ø                | Ø                | 0                | 1                | 1                | 1                | 0                | 1                |

| Ø                | Ø                | Ø                | Ø                | Ø                | Ø                | 0                | 1                | 1                | 1                | 1                | 0                | 0                |

| Ø                | Ø                | Ø                | Ø                | Ø                | 0                | 1                | 1                | 1                | 1                | 0                | 1                | 1                |

| Ø                | Ø                | Ø                | Ø                | 0                | 1                | 1                | 1                | 1                | 1                | 0                | 1                | 0                |

| Ø                | Ø                | Ø                | 0                | 1                | 1                | 1                | 1                | 1                | 1                | 0                | 0                | 1                |

| Ø                | Ø                | 0                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 0                | 0                | 0                |

| Ø                | 0                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 0                | 1                | 1                | 1                |

| 0                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 0                | 1                | 1                | 0                |

Les sorties du 74147 sont normalement à 1 quand aucune des entrées n'est a son niveau vrai cesi correspond à la condition d'entrée du chiffre décimal 0, pour obtenir le code BCD naturel à partir des sorties du 74147 il faut ajouter un inverseur à chacune des sorties

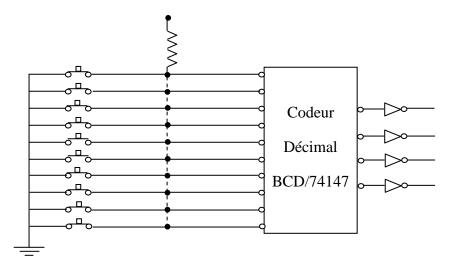

## III.2.2 Codeur d'interrupteur

Dans la figure suivante on montre comment on peut réaliser avec le circuit intégré 74147 un codeur d'interrupteur

Les interrupteurs sont du type ouvert au repos de sorte que les entrées du codeur sont généralement toute à 1 quand c'est le cas la sortie BCD est (0000). Quand une touche est enfoncée (interrupteur) le circuit donne en sortie le code BCD correspondant a ce chiffre.

Le codeur interupteur peut servir toutes les fois que l'on doit introduire manuellement des données BCD dans un système numérique. Un exemple parfait de cela est la calculatrice éléctronique dans laquelle un opérateur introduit un nombre décimal en appuyant succéssivement sur les interrupteurs du clavier

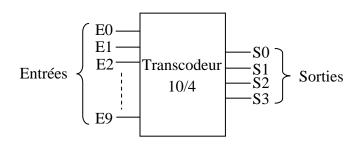

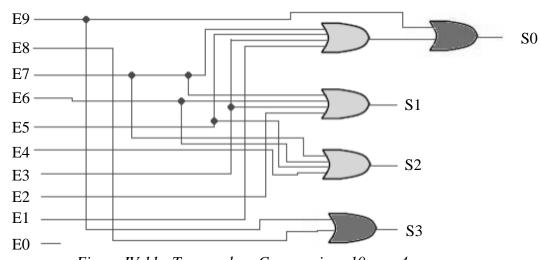

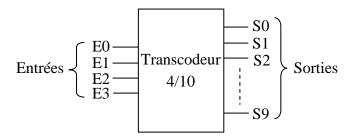

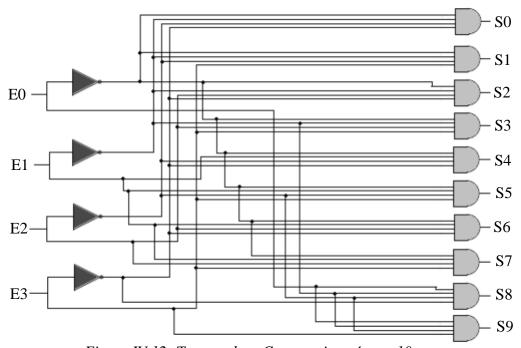

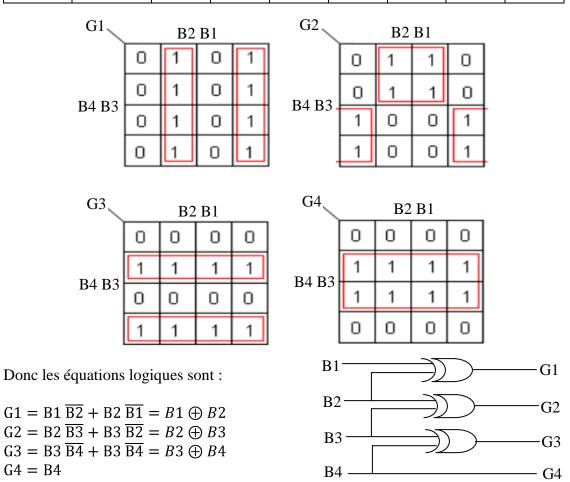

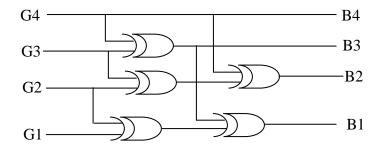

#### IV. Les transcodeurs

Un transcodeur (convertisseur de codes) est un dispositif permettant de passer du nombre N écrit dans le code C1 au même nombre N écrit dans le code C2. L'utilisation des transcodeurs est relativement limitée, ce qui explique qu'on ne les trouve pas tous sous forme de circuits intégrés : il faut alors les réaliser à l'aide de portes logiques ET-NON, OU NON ... etc.

La réalisation pratique d'un transcodeur passe par sa table de vérité, puis par l'écriture et la simplification des équations de sorties avec les tableaux de Karnaugh.

Parmi les transcodeurs que l'on trouve en circuits intégrés, on peut citer :

- les transcodeurs décimal / BCD (circuit 74147).

- les transcodeurs BCD / décimal (circuits 7442, 7445, et 4028).

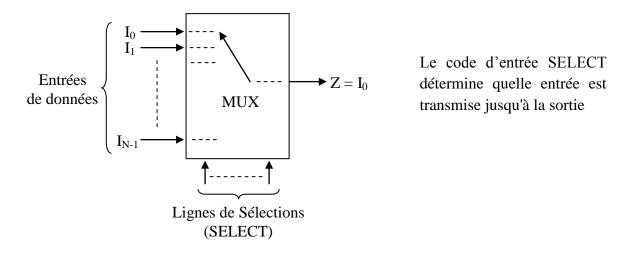

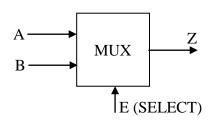

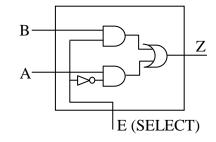

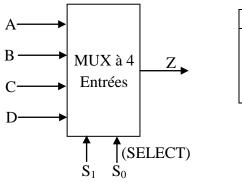

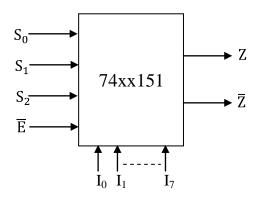

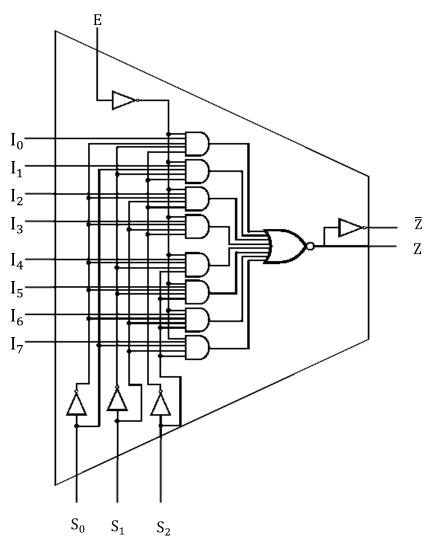

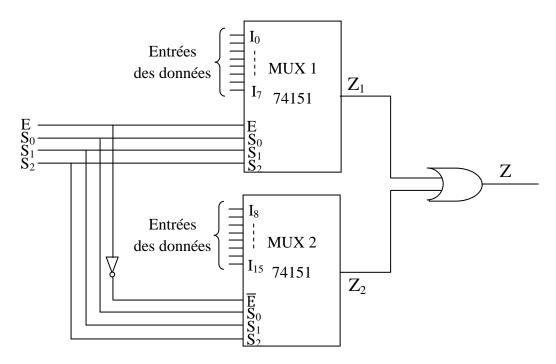

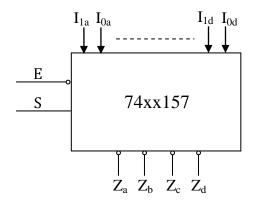

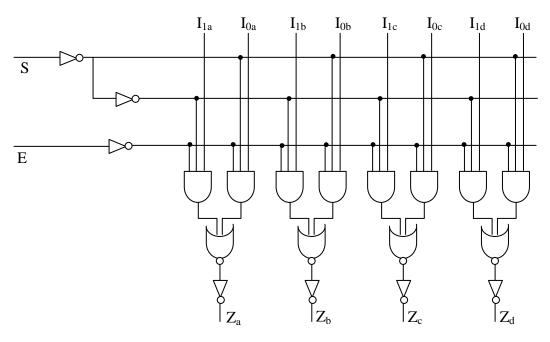

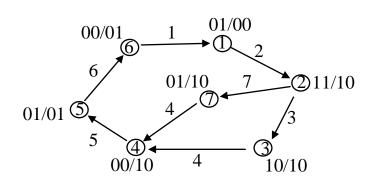

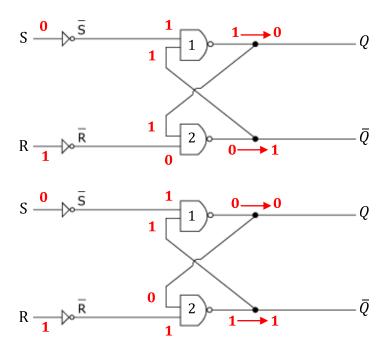

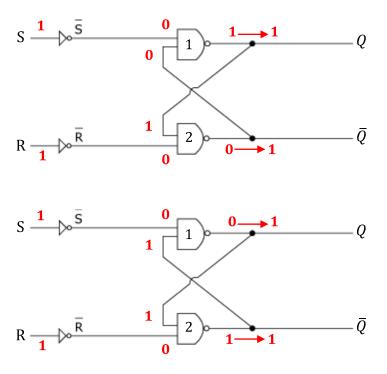

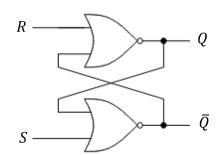

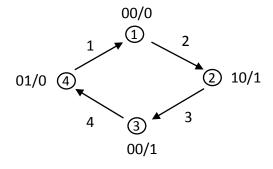

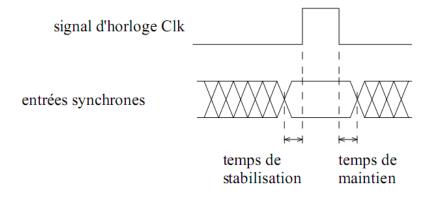

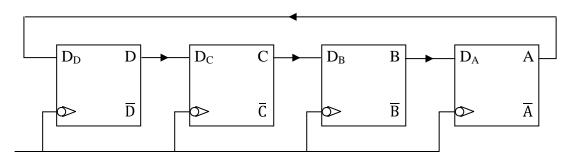

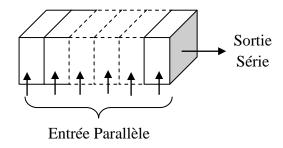

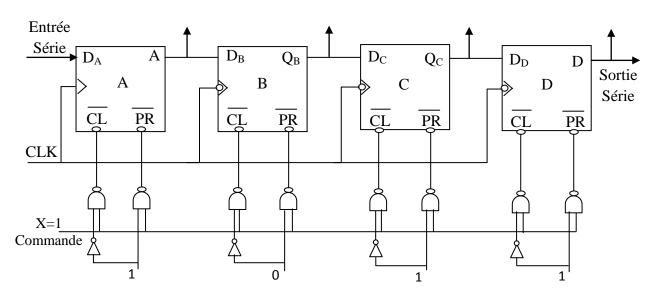

- les transcodeurs XS 3 / décimal (circuit 7443).